# STM32+CycloneIV 統合ボードⅡ

## マニュアル

株式会社日昇テクノロジー

<http://www.csun.co.jp>

info@csun.co.jp

作成日: 2015/1/22

copyright@2015

## 目 次

|                               |    |

|-------------------------------|----|

| 1. 概要 .....                   | 3  |

| 2. HW 配置図 .....               | 4  |

| 3. コアボードの HW 配置図 .....        | 7  |

| 4. ARM ダウンロード変換基板 .....       | 9  |

| 5. FPGA ダウンロード変換基板 .....      | 10 |

| 6. 電源と電圧基準 .....              | 11 |

| 7. クロックシステム .....             | 12 |

| 8. SPI Flash .....            | 13 |

| 9. SRAM .....                 | 14 |

| 10. SDRAM .....               | 15 |

| 11. FPGA コンフィギュレーションモード ..... | 16 |

| 12. ARM 拡張 I/O .....          | 17 |

| 13. FSMC スペース拡張 .....         | 18 |

| 14. FPGA 拡張 I/O .....         | 19 |

| 15. その他のリソース .....            | 20 |

| 16. 実験基板 .....                | 21 |

## 1. 概要

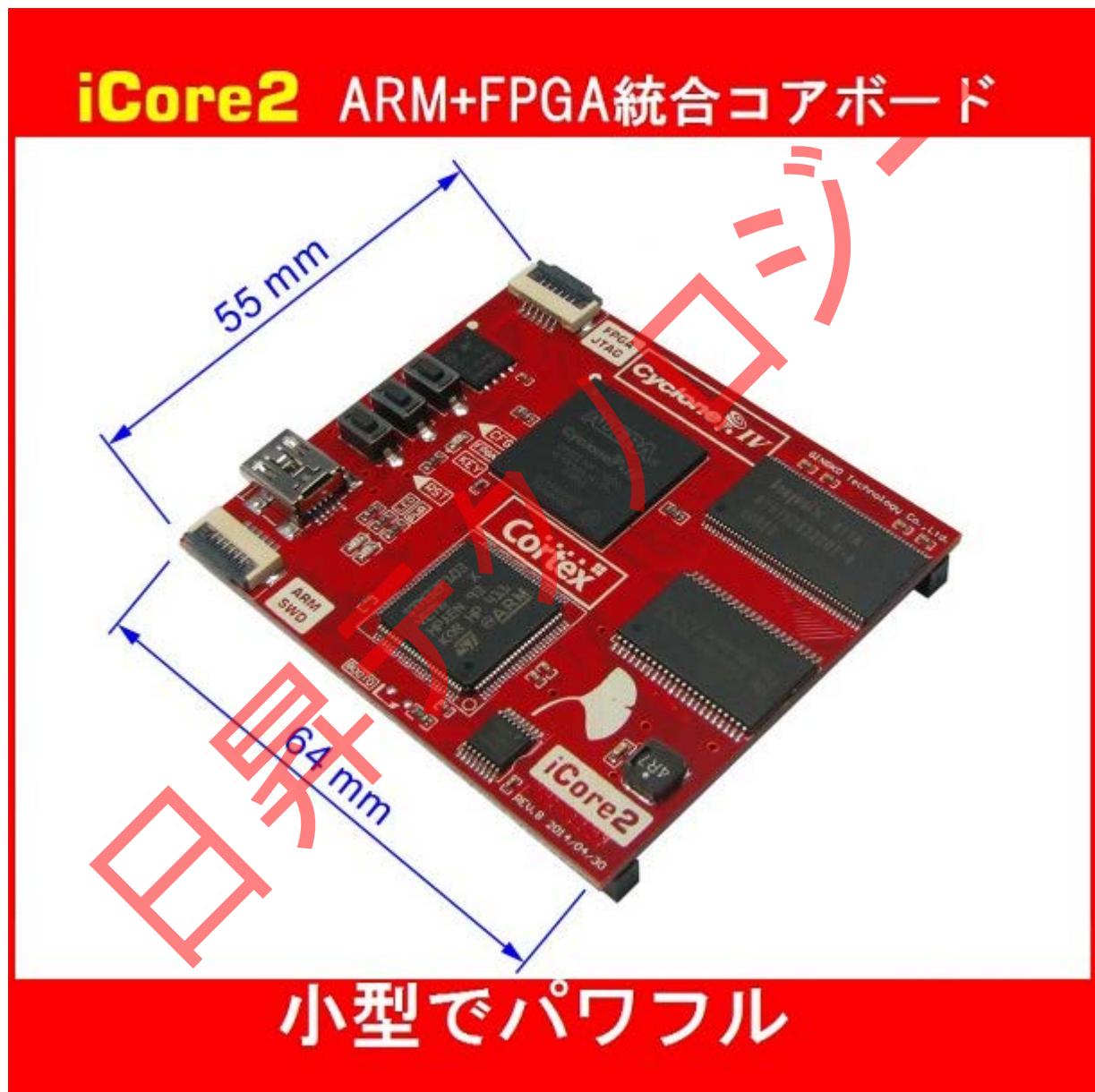

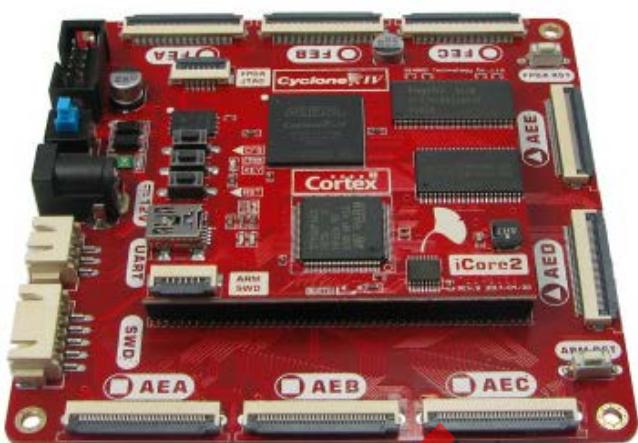

iCore2はARM&FPGAの二つの機器を含むデュアルコアプレートである。ARMはSTMicroelectronics の高性能である32位Cortex-M3カーネルSTM32F103VEマイクロプロセッサを採用し、周波数が72MHzである。外付けインターフェースも満載され、最新のCycloneTM IVであるFPGA EP4CE10F17C8Nも採用される。iCore2はARM、FPGAをメインプロセッサ、コプロセッサとしてパラレルバスでパラレルケースの処理を行う。その動作モードはARM、FPGAを相互補完して組込みシステムに両方のメリットを協力作業の中で完全に発揮させることができる。

iCore2 STM32+CycloneIVコアボードIIの実物図

## 2. HW 配置図

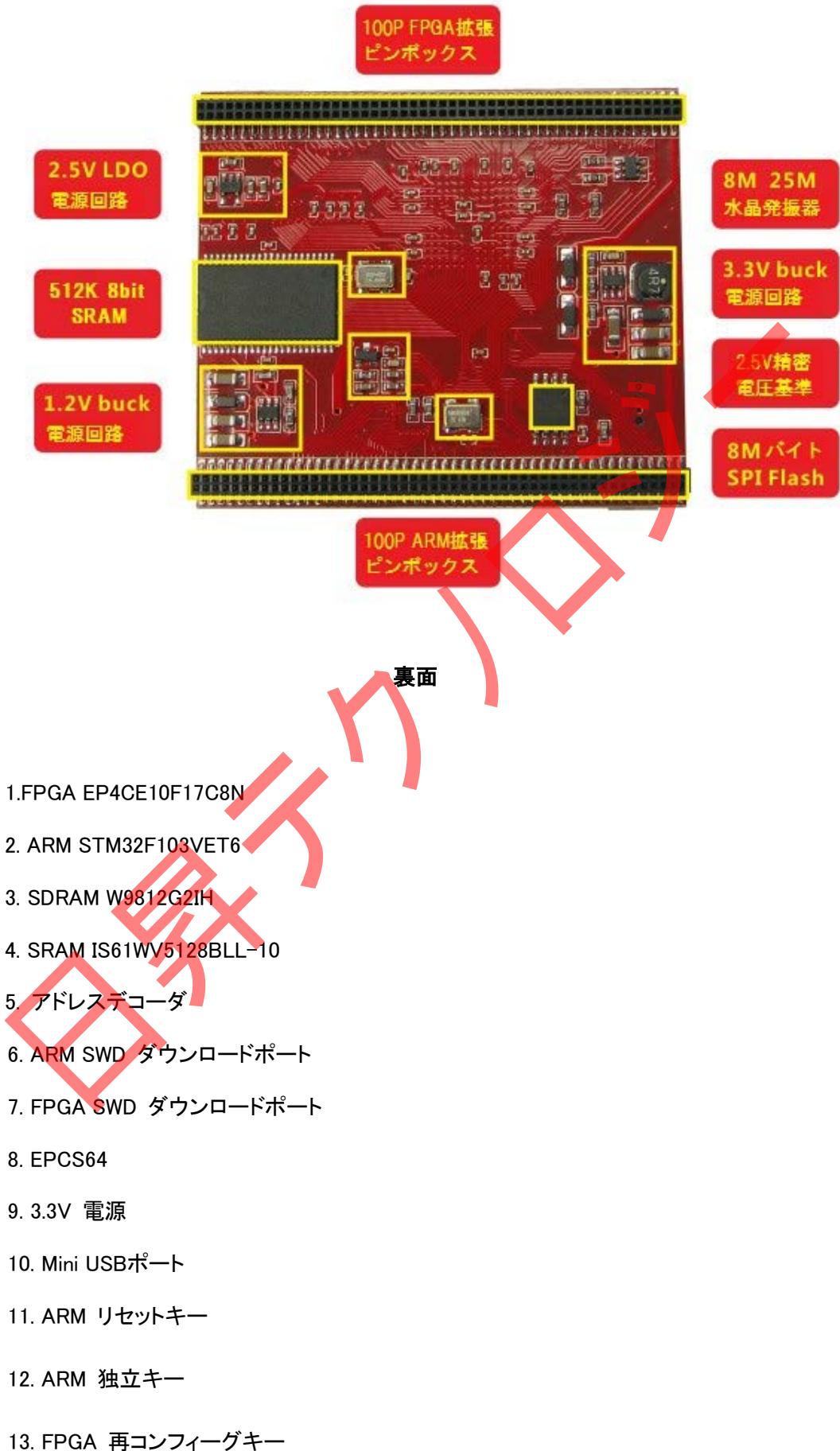

14. 50X2P ARM 拡張I/O

15. 50X2P FPGA 拡張 I/O

16. SRAM IS61WV5128BLL-10

17. W25Q64 8M flash

18. 8M アクティブ・クリスタル

19. 25M アクティブ・クリスタル

20. 1.2V電源

21. 2.5V電源

日昇テクノロジー

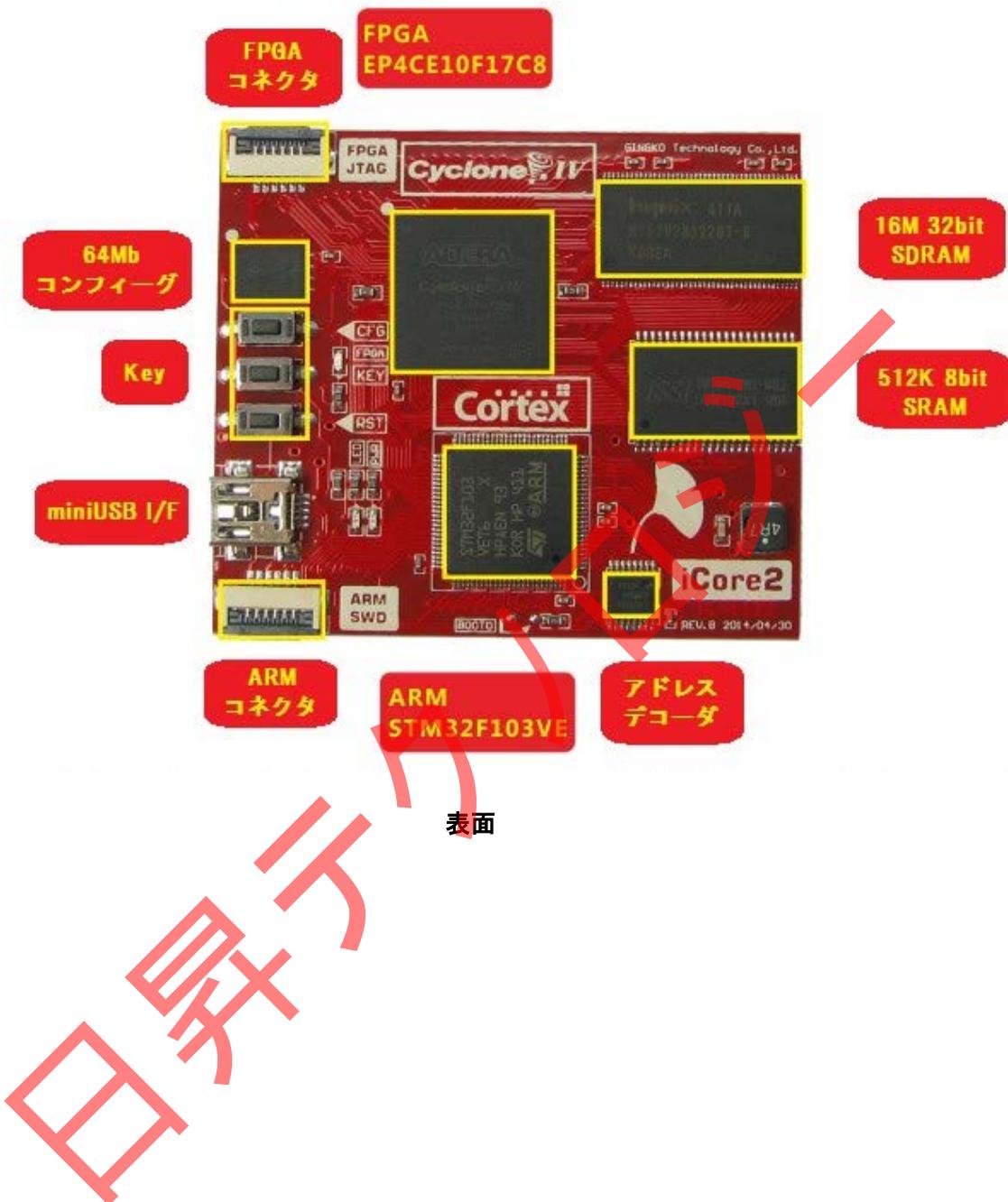

### 3. コアボードのHW配置図

表一:コアボードのHW配置

| 分類         | 名称              | 特性                         |

|------------|-----------------|----------------------------|

| ARM<br>関連  | 型番              | STM32F103VET6              |

|            | パッケージ           | TQFP100                    |

|            | Basic frequency | 72MHz                      |

|            | FLASH           | 512KHz                     |

|            | RAM             | 64K                        |

|            | FMSC            | 1                          |

|            | 汎用タイマー          | 4                          |

|            | 高級タイマー          | 2                          |

|            | 基本タイマー          | 2                          |

|            | SPIインターフェース     | 3                          |

|            | I2Cインターフェース     | 2                          |

|            | USARTとUART      | 3+2                        |

|            | USB Full Speed  | 1                          |

|            | CAN             | 1                          |

| FPGA<br>関連 | 12位ADR          | 3(16/バス)                   |

|            | 12位DAC          | 2                          |

|            | GPIO            | 80                         |

|            | ダウンロードポート       | オンボードSWDポート                |

|            | 型番              | EP4CE10F17C8N              |

|            | パッケージ           | BGA256                     |

|            | M9Kレジスターブロック    | 46                         |

|            | M9K総容量          | 414Kbit                    |

|            | 18*18アナログ乗算器    | 23                         |

|            | PLL             | 2                          |

|            | I/O数量           | 179                        |

|            | コンフィギュレーションチップ  | EPCS64<br>容量 64MBit/8Mbyte |

|            | ダウンロードポート       | オンボードJTAGダウンロード            |

続表一:コア板のHW配置

| 分類     | 名称                 | 特性                                                    |

|--------|--------------------|-------------------------------------------------------|

| タイマー   | ARMタイマー            | 8Mアクティブ・クリスタル                                         |

|        | FPGAタイマー           | 8Mアクティブ・クリスタル                                         |

|        | FGPAタイマー           | 8Mアクティブ・クリスタル、ARMと共に                                  |

| メモリ拡張  | FLASH拡張SDRAM       | W9812G2IH-6<br>32位の幅<br>容量 16MBit                     |

|        | FLASH拡張SRAM        | IS61WV5128BLL-10TLI 2枚<br>2枚を組み合わせて16位となる<br>容量 1MBit |

|        | FPGAコンフィギュレーションチップ | EPCS64<br>容量 8MBit                                    |

|        | ARM拡張SPI Flash     | W25Q64<br>容量 8MBit                                    |

| 電源システム | 入力特徴               | 拡張とUSBポートのダブル入力ポート<br>幅電圧範囲 5~12V                     |

|        | 3.3V               | MP2359<br>1.2A BUCK チップ                               |

|        | 2.5V               | RT9193-25B<br>LDO電圧レギュレータ                             |

|        | 1.2V               | MP2359<br>1.2A BUCK チップ                               |

|        | 電圧基準               | TL431A 2.5V基準                                         |

| 拡張性能   | ARM IO             | 72<br>(24のFSMCバスを含む)                                  |

|        | FPGA IO            | 80<br>(SDRAMと共に26個を含む)                                |

|        | ARM FSMCバス空間       | CS1~CS3の三つの片選空間                                       |

| その他    | USBインターフェース        | (24のFSMCバスを含む)                                        |

|        | LED                | ARM/FPGA 一つずつ                                         |

|        | キー                 | FPGA再コンフィギュレーションキー、ARMリセット、ARM独立キー                    |

## 4. ARM ダウンロード変換基板

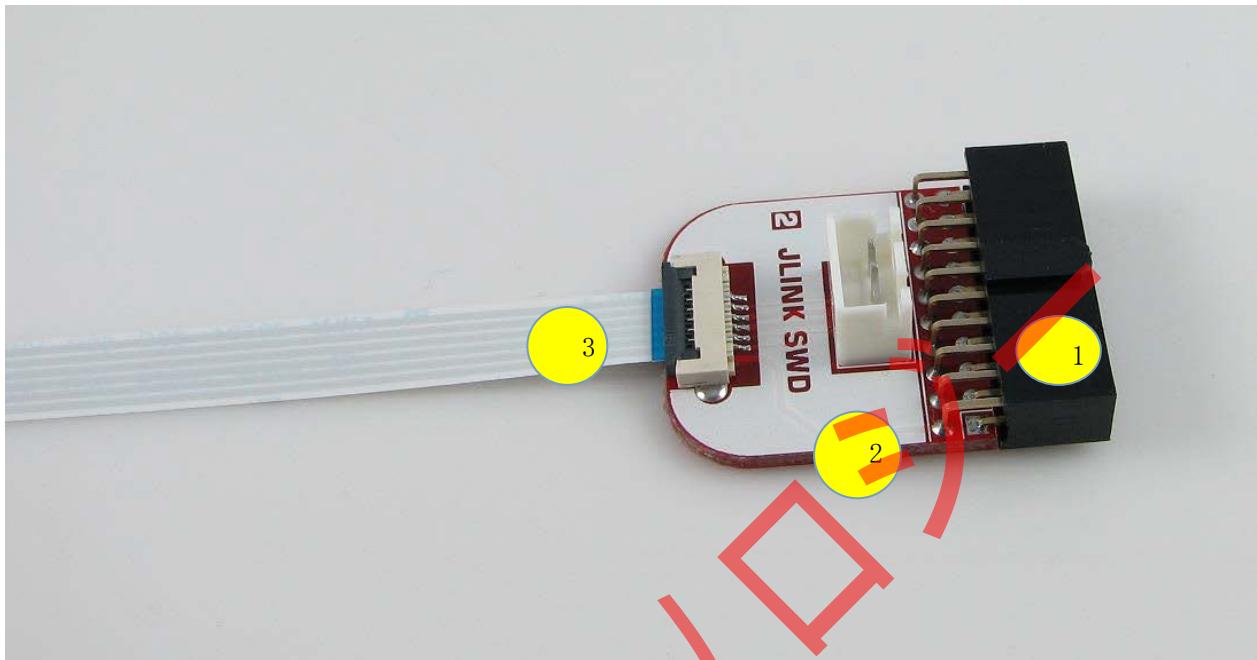

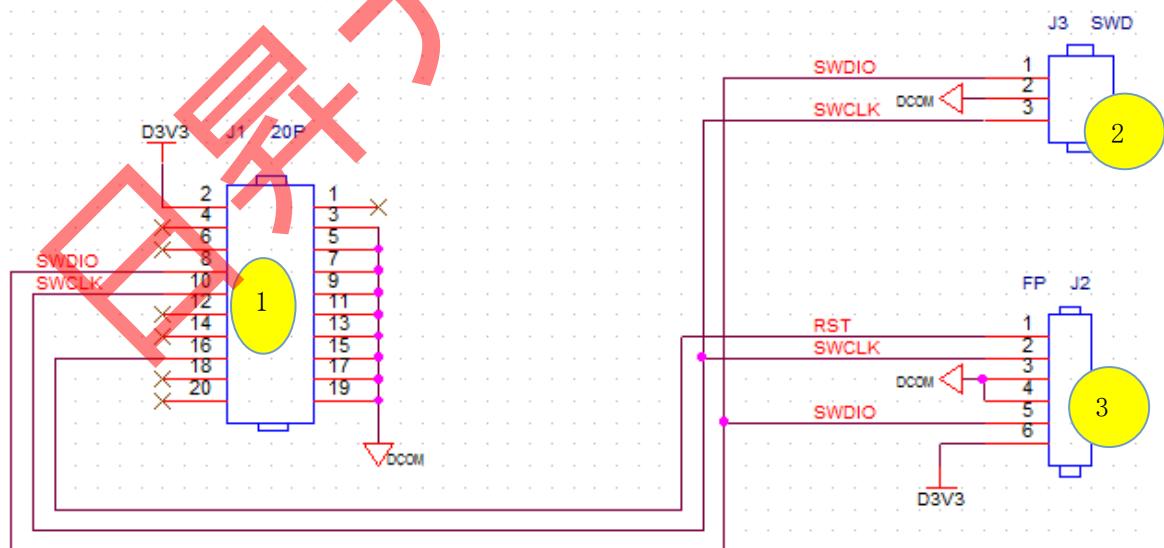

使いやすさとサイズのバランスを考慮した上、ARM SWDダウンロード変換基板を設計したので、icore2コアボードのSTM32向けのアプリのダウンロードが容易になった。その変換基板に三つのインターフェースが含まれている。画像参照：

1.20P ヘッダは弊社の [USB Open Link\(多インターフェース搭載、高速 JTAG\)](#) に接続できる

2.3PXH2.54 台座は弊社の [持ちやすい高速 JTAG-MiniLink](#) または市販の STLINK/V2 との接続に使う

3.6P FPCコネクタとケーブルはコアプレートフォームの接続に使う。ケーブルの接点面を下に、青い面を上に向けて挿入する。FPCは折りたたみ式で、コネクタが小さく精密なので、操作時、強い力を加えないよう、扱い方には十分ご注意ください。

## 5. FPGA ダウンロード変換基板

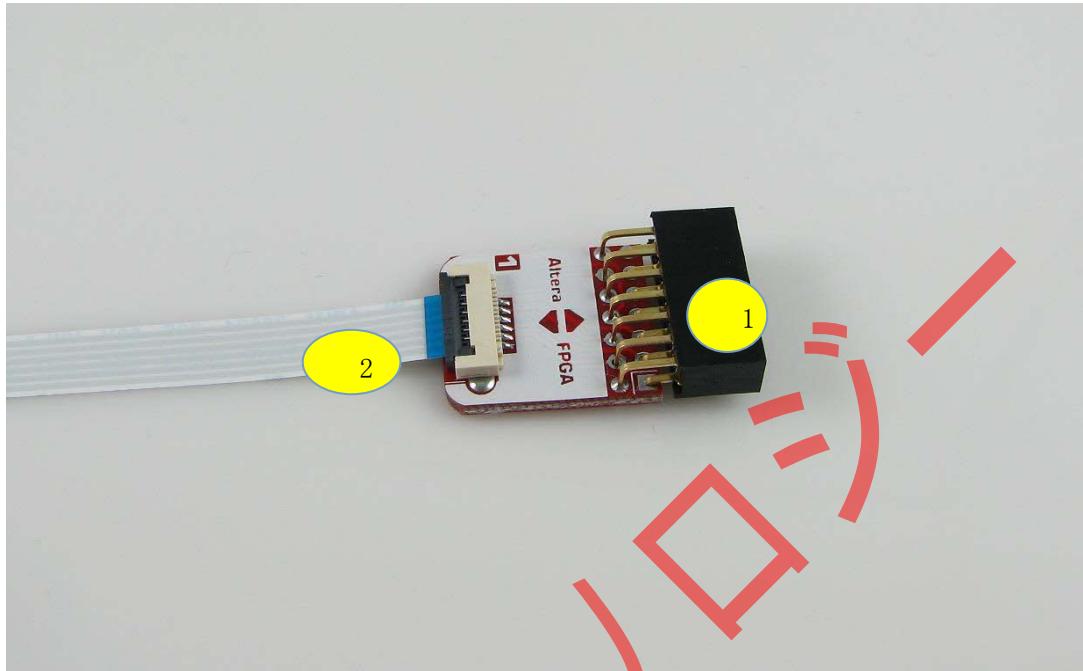

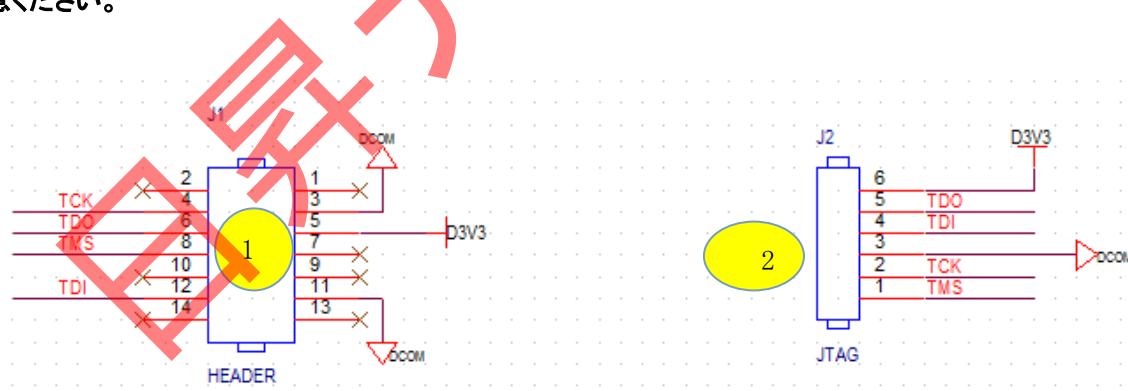

同様に便利さとサイズのバランスを考慮した上、FPGA JTAGダウンロード変換基板を設計したので、icore2コアボードのFPGA向けのアプリケーションのダウンロードが容易になった。変換基板には二つのインターフェースが含まれている。画像参照：

1.10P ヘッダが弊社の [ALTERA CPLD/FPGA 用のダウンロード・ケーブル](#)に接続できるが、ポラリティ装置が設けられていないので、変換基板の正面と USB Blaster の正面と必ず一致させて接続すること。

2.6P FPCコネクタとケーブルはコアプレートフォームとの接続に使う。ケーブルの接点面を下に、青い面を上に向けて挿入する。FPCは折りたたみ式で、コネクタが小さく精密なので、操作時、強い力を加えないよう、扱い方には十分ご注意ください。

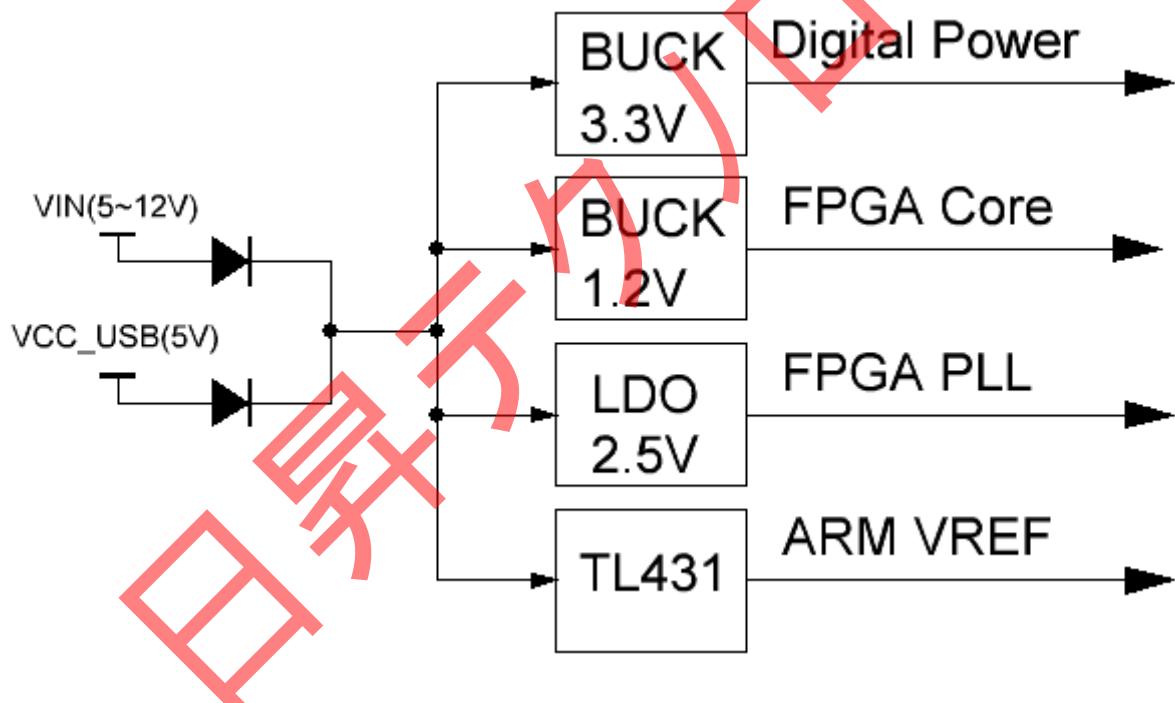

## 6. 電源と電圧基準

使いやすさと実用性を考慮し、icore2はデュアル入力電源システムを採用している。ユーザーがUSBインターフェースまたは拡張ピンヘッダーでの電力入力方式で給電できる。それにその二つの方法が共存できる。小さいシステムであるが、icore2は高品質の電源を必要とする。電源の効率、性能を両立させるため、下記の4つの方面でシステムへの電力を供給し、それに対する基準も提供する。

1. **デジタル電源**: デジタル電源は出力が3.3Vである。高効率のBUCK回路を採用し、ARM / FPGA / SDRAM / SRAMなどの給電を行う。BUCKチップの出力電源は1.2Aで、システムの定額電流を大幅に超えている。

2. **FPGAカーネル電源**: FPGAカーネルは1.2Vの給電方式を採用している。高効率のBUCK回路も利用。

3. **FPGA PLL電源**: FPGA PLLに大量のアナログ回路が含まれている。PLLの性能を確保するには、LDOでPLLにアナログ電源を入力する。この電源部分の出力電圧は2.5Vである。

4. **ARMアナログ電圧基準**: STM32F103VE は独立のアナログ電圧基準、片上ADC/DACへの基準電圧を提供する。ここにTL431でADC/DACに2.5Vの基準電圧を提供する。

icore2電源及び電圧基準システム流れ図

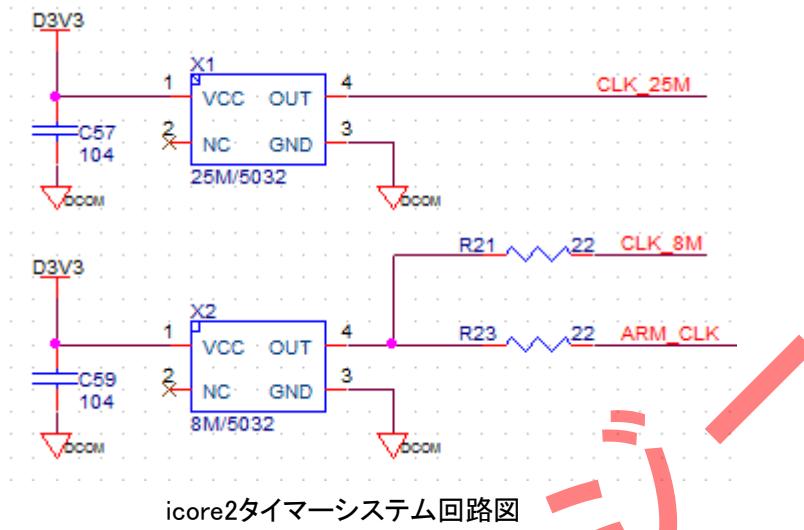

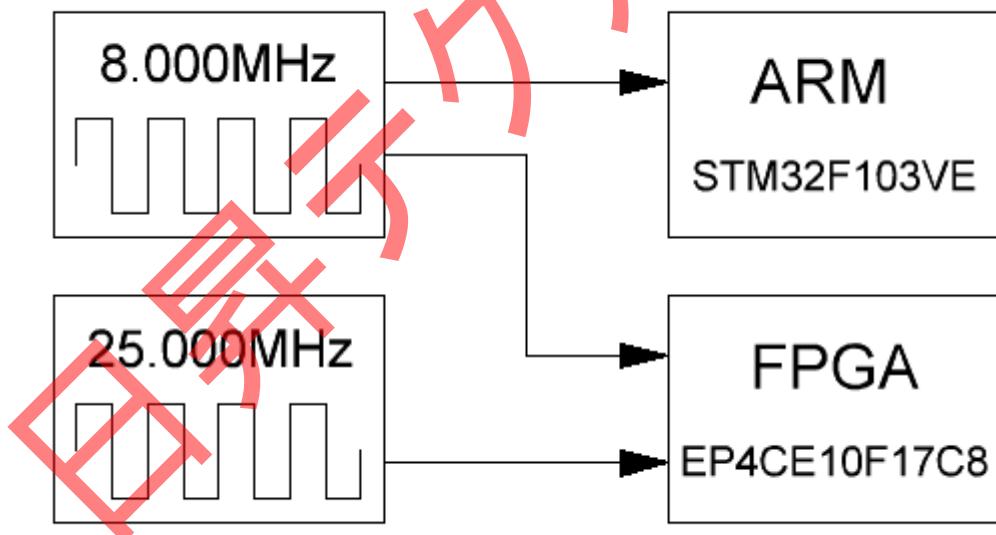

## 7. クロックシステム

icore2コアプレートフォームにアクティブ・クリスタルクロックが二つ含まれていて、8Mと25MHzである。

アクティブ・クリスタルはARMとFPGA動作時の安定性を確保し、クロックの障害防止を保証できる。FPGAは異なる周波数のクロックを二つ入力することで、クロックが要求する更に複雑なタイミングにも適応する。二つのアクティブ・クリスタルのARM/FPGAとの接続図

icore2タイマーシステム流れ図

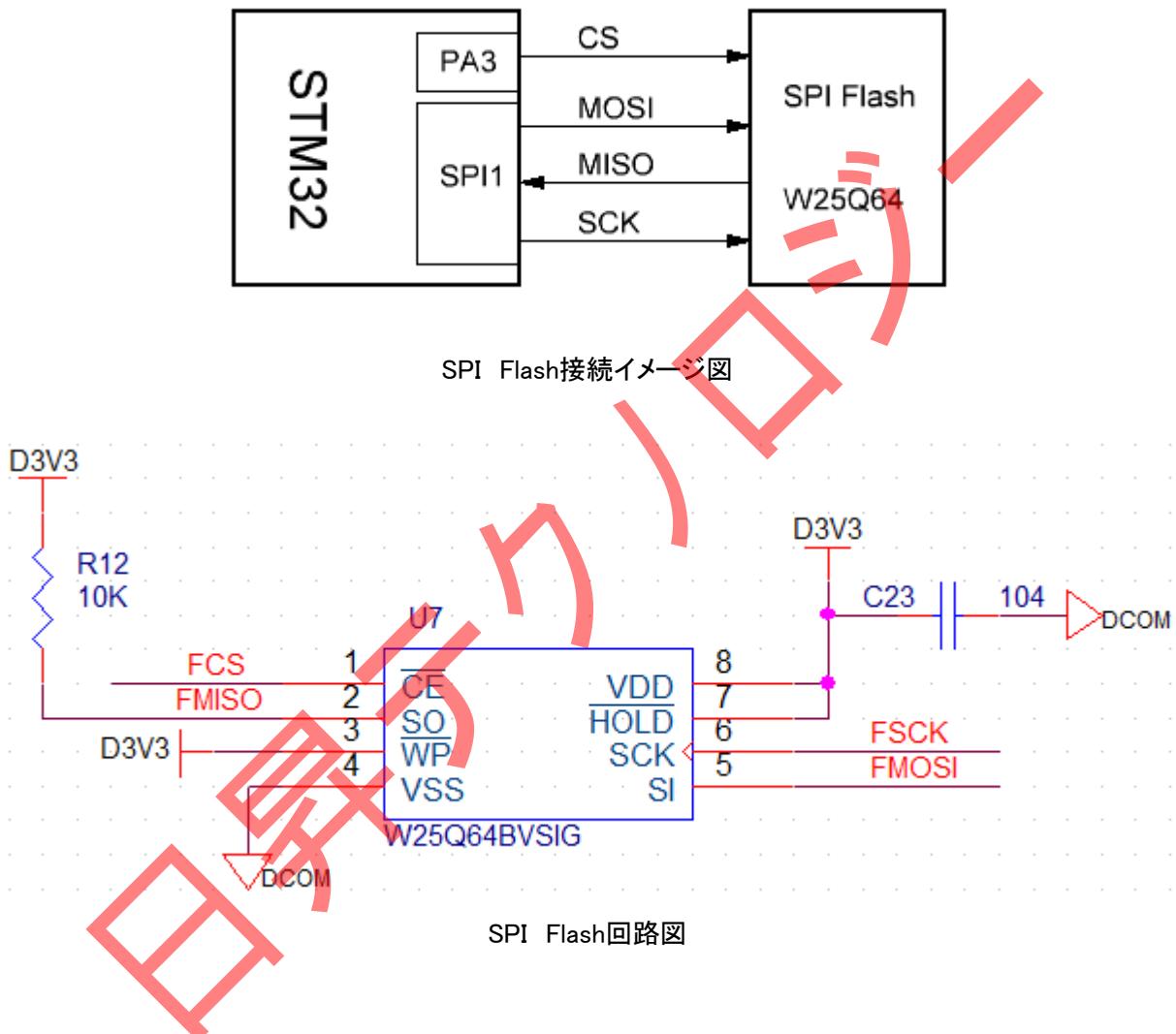

## 8. SPI Flash

icore2プレートフォームにSPI Flashが一枚搭載され、データ、フォント、コンフィギュレーションなどの保存に使う。型番はW25Q64で、容量は8M Byteである。セクターはサイズが4096で、合計が2048個のセクターである。ソフトウェア上では、FatfsソフトウェアパッケージをSPI Flashのドライバーとして、USBインターフェースでSPI FlashをバーチャルUSBメモリと見られることで、コンピュータでのファイルの管理は容易になる。

icore2 SPI Flashの接続図と回路図：

## 9. SRAM

iCore2 プレートフォームに SRAM が 2 枚搭載され、データキャッシュに使う。その型番は IS61WV5128 で、一枚の容量は 512k byte、8 位で、2 枚で 1M byte、16bit となる。二枚共に FPGA に接続されている。SRAM は簡易なインターフェースと高スピードのメリットを持っているが、価格も高い。

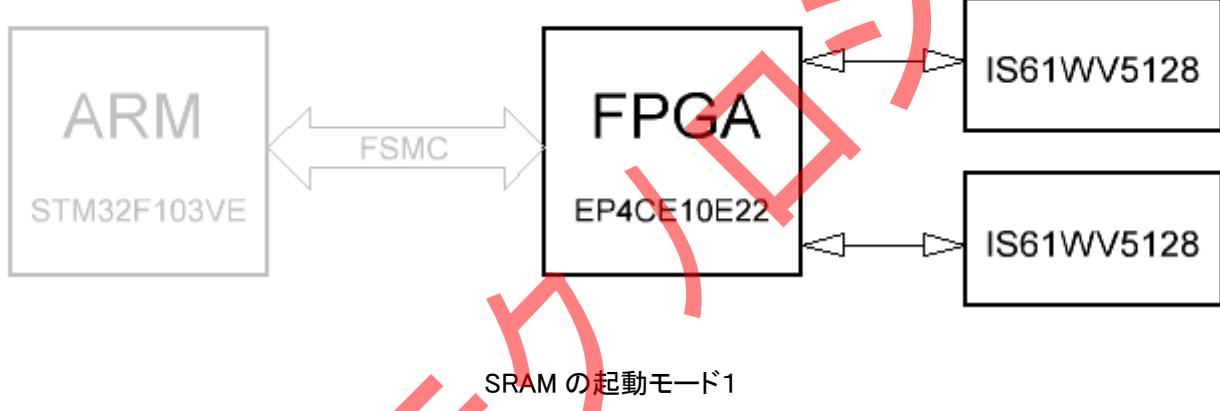

iCore2 システムに SRAM が二つの動作モードがある。

**モード1**: FPGA による直接駆動。このモードで SRAM を FPGA がコントロールするキャッシュとして、データ採集のキャッシュなどの分野に使う。

**モード2**: FPGA をブリッジとして、SRAM が STM32 の FSMC バスと繋がる。このモードで SRAM は STM32 の拡張メモリとなる。応用の詳細は iCore2 のサンプルソースをご参考ください。

### MODE 1

SRAM の起動モード1

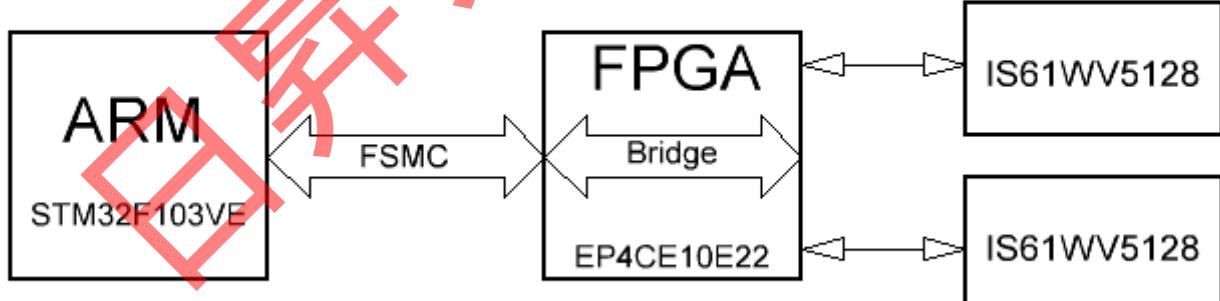

### MODE 2

SRAM の動作モード2

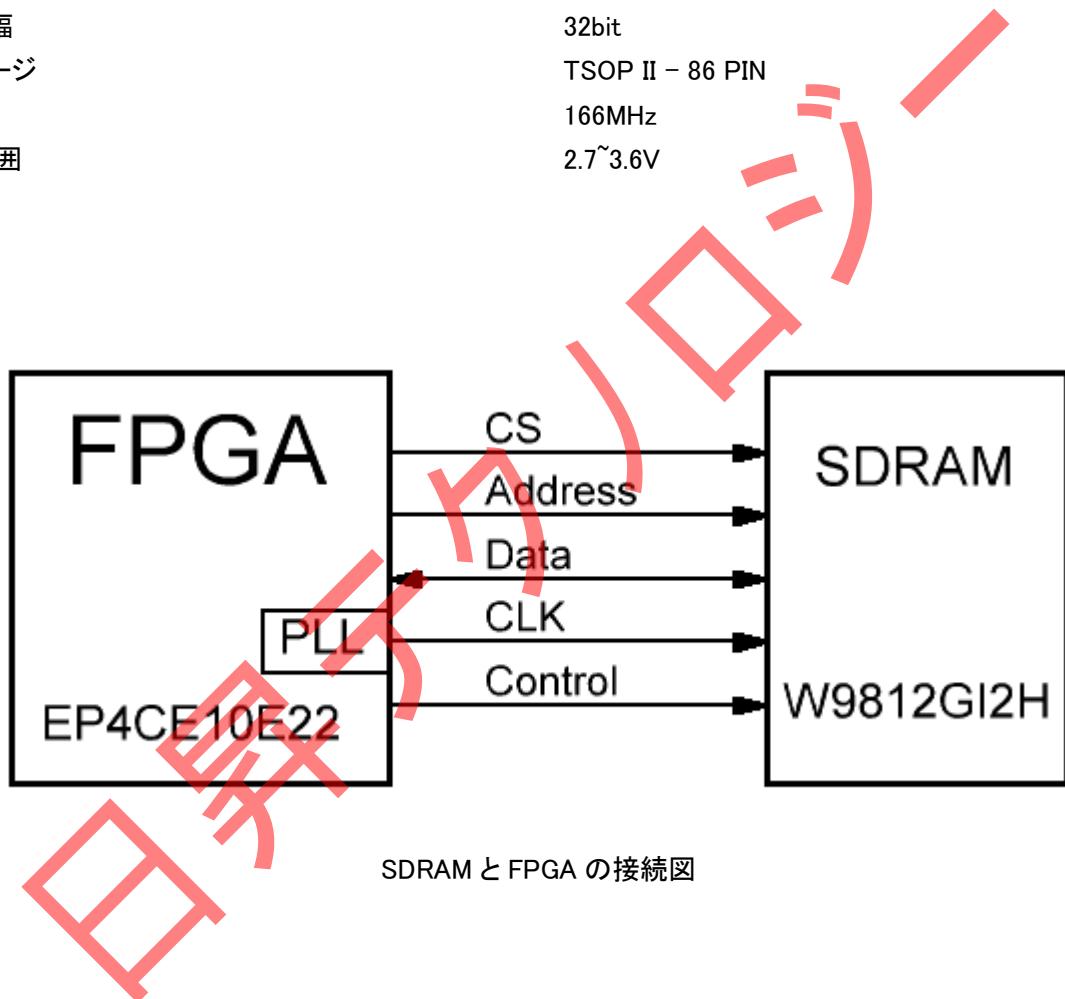

## 10. SDRAM

iCore2プレートフォームにSDRAMが1枚搭載され、その型番はW9812G2IHである。データキャッシュまたはNIOSIIソフトカーネルが内蔵された場合、そのSDRAMをNIOSIIのメインメモリとして使う。SDRAMは容量が大きく、データ帯域も幅広い(32位で、普通は16位)である。ただし駆動が複雑で使用するには不便である。

SDRAMの具体的な基準は下記の通り:

|       |                                 |

|-------|---------------------------------|

| 型番    | W9812G2IH-6                     |

| 容量    | 1M X 4 BANKS X 32bit = 16M Byte |

| BANK  | 4 BANKS                         |

| データ幅  | 32bit                           |

| パッケージ | TSOP II - 86 PIN                |

| 速度    | 166MHz                          |

| 電圧範囲  | 2.7~3.6V                        |

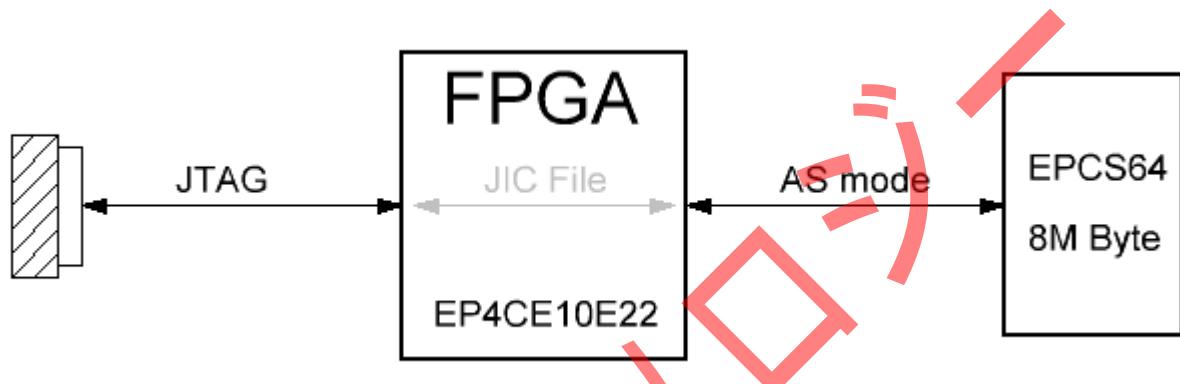

## 11. FPGA コンフィギュレーションモード

icore2プレートフォームに搭載されたFPGAはSRAM構造なので、電源を入れる場合、ファームをロードして起動しなければならない。ファームをFPGAのSRAMにロードする方法は二つある。

**方法1:** JTAGモードでUSB Blasterダウンローダーを利用してFPGAにダウンロードする。その操作方法は簡単であるが、電源を切ると消えるので、通常デバッグでよく使われる。

**方法2:**搭載されているEPCS64でFPGAをコンフィギュレーションする。電源を入れ、ASモードでEPCS64に保存されたコードをFPGAにロードする。

FPGA コンフィギュレーションモード図

JTAGでファームをEPCS64にロードする時のステップ:

Step 1: QuartusIIに内蔵されたコンバーターでSOFファイルをJICファイルにコンバートする

Step 2: JTAGインターフェースでJICファイルをEPCS64にダウンロードする。それなら、電源を切っても、FPGAのファームロードについての心配がなくなる。

システムにNIOSIIプロセッサを利用する場合、同様にNIOSIIのソースコードのターゲットファイルをEPCSに保存することもできる。

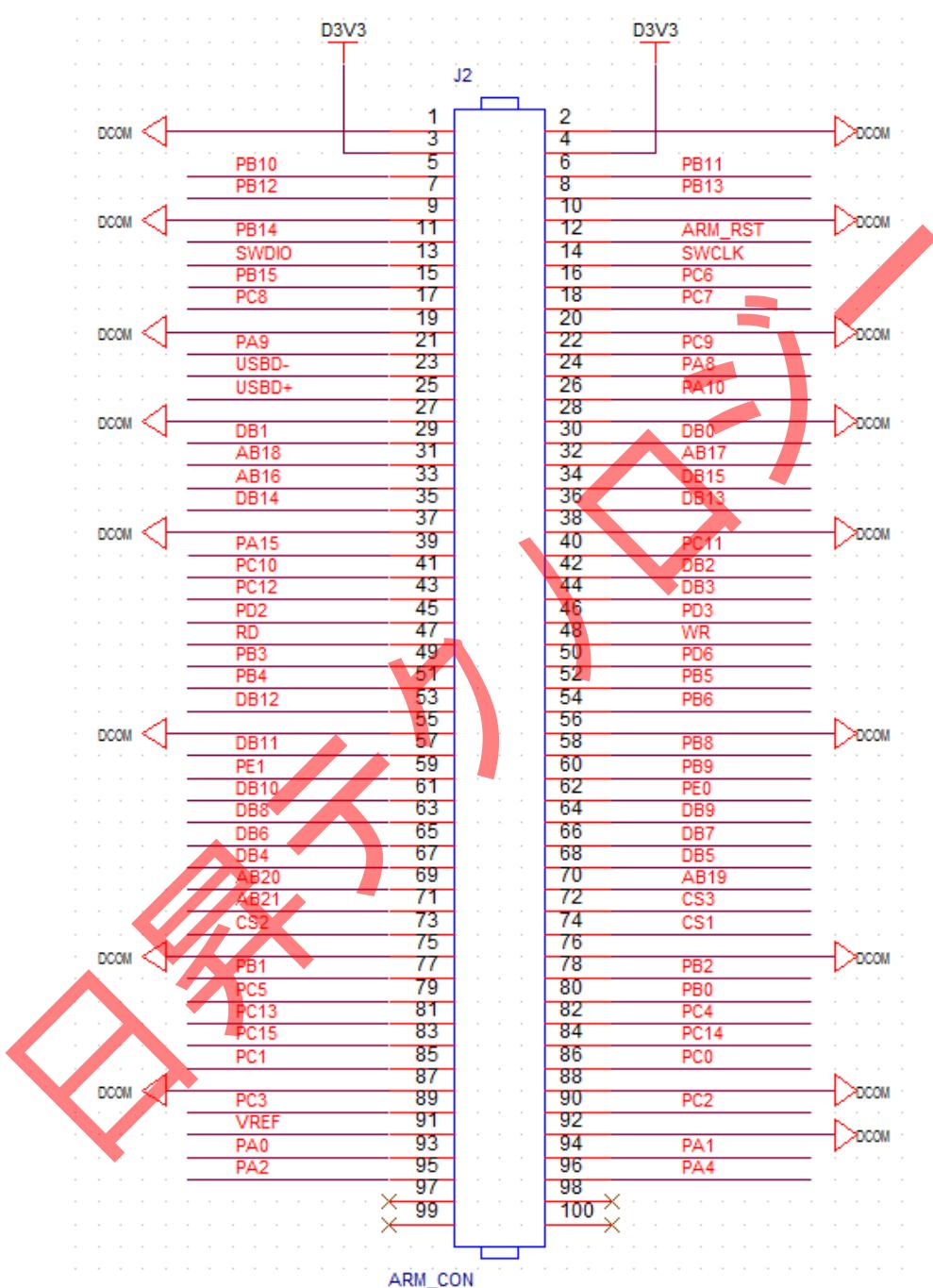

## 12. ARM 拡張 I/O

icore2プレートフォームに搭載されたARMプロセッサはリソースが豊富で、プレートフォームでFPGAと接続する他、ARMはユーザーのためにI/Oを若干拡張して、その中にFSMCバスも含んでいる。回路図：

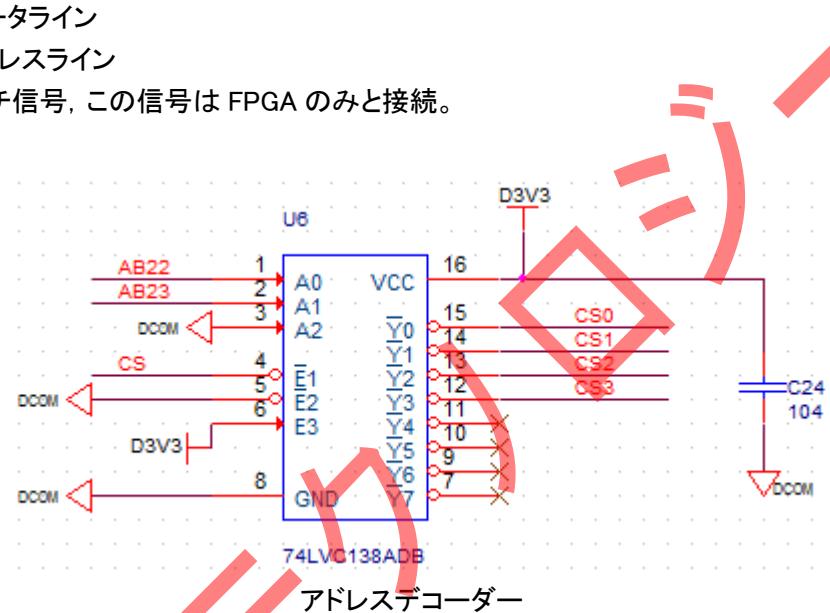

## 13. FSMC スペース拡張

FSMC (Flexible Static Memory Controller、可変スタティックストレージコントローラ)とは STM32 外部バスの拡張のことである。SRAM/FLASH と外部バス特徴を持っているペリフェラルと接続できる。

icore2 はアドレススペースデコード技術を利用して、4つの CS スペースを拡張した。CS0~CS3 である。そのうち、CS0 は FPGA に繋がり、CS1~CS3 の三つは外付けにする。FSMC に必要なピンは下記の通り：

- CS1~CS3: 三つの独立した CS スペース

- WR: 書き込イネーブル、低レベルで有効

- RD: 読み込イネーブル、低レベルで有効

- DB[15:0]: 16bit データライン

- AB[21:16]: 6bit アドレスライン

- NADV: アドレスラッチ信号、この信号は FPGA のみと接続。

CS1~CS3 のベースアドレススペース：

CS1: (0x60000000 + (1 << 23))

CS2: (0x60000000 + (2 << 23))

CS3: (0x60000000 + (3 << 23))

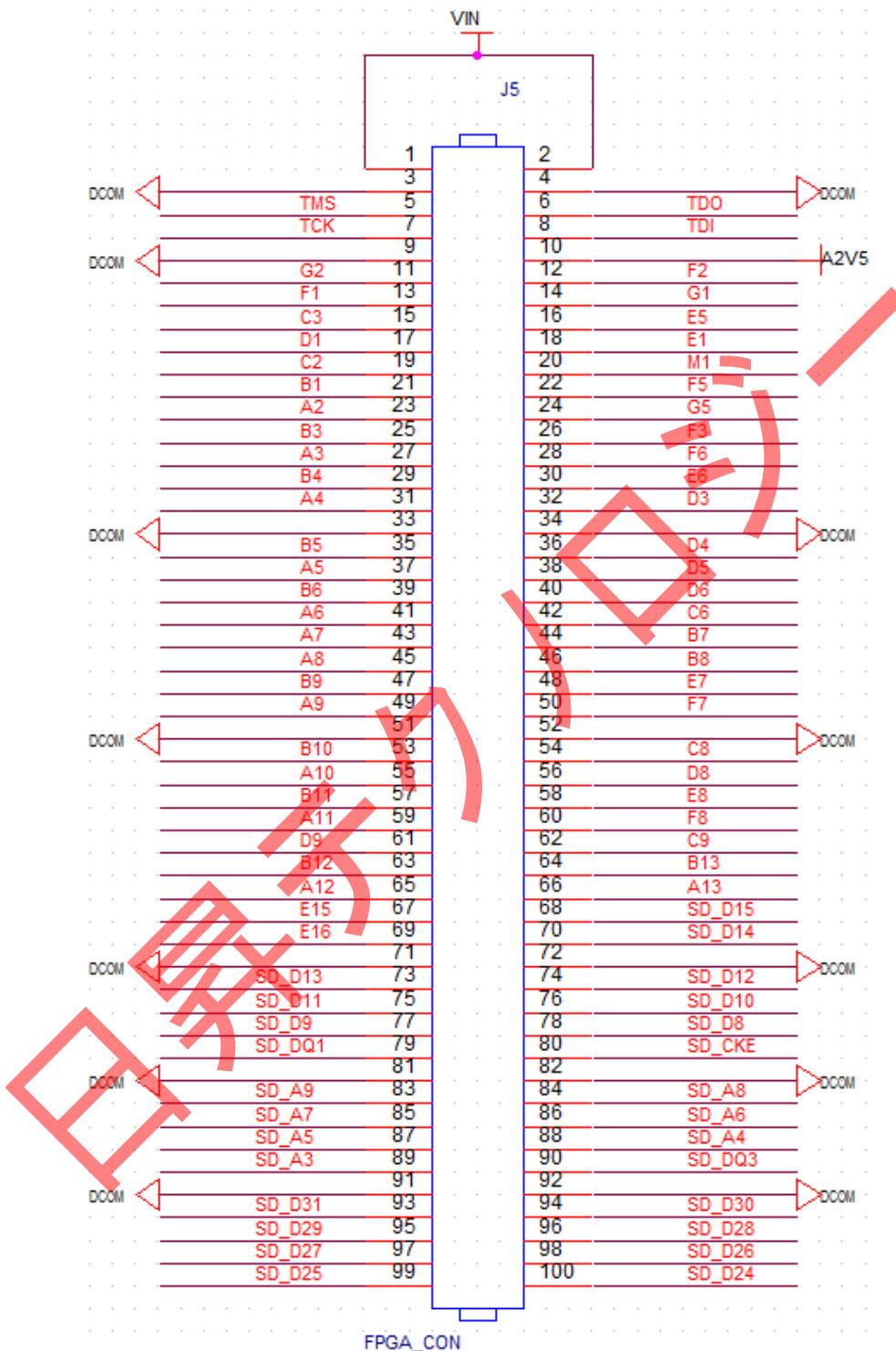

## 14. FPGA 拡張 I/O

iCore2 プレートフォームに搭載された FPGA 拡張 I/O: (VIN は入力電源である)

## 15. その他のリソース

通常デバッグの便利さを考慮して、icore2 プレートフォームにいくつかのキーと LED を搭載した。そのリソースの配分は下記の通り：

□ 電源LEDランプ、3.3Vに接続

□ ARM緊急リセットキー、ARMリセットピンに接続

□ 二つの独立キー、ARMのPC8に接続

□ 二つのLEDランプ、ARMのPC7に接続

□ 二つのLED、FPGAのJ6に接続。

□ 独立USBインターフェース、システムに電気を入力する働きの他、STM32のUSBインターフェースとの接続でUSB通信を行う働きがある。

□ FPGA再コンフィギュレーションキー、そのキーの押下でEPCS内のファームを再度FPGAにロードできる。

icore2プレートフォームに搭載されたインターフェース、キーなどは精密的な部品なので、ご利用の場合、破損がないように、取り扱いには十分ご注意ください。

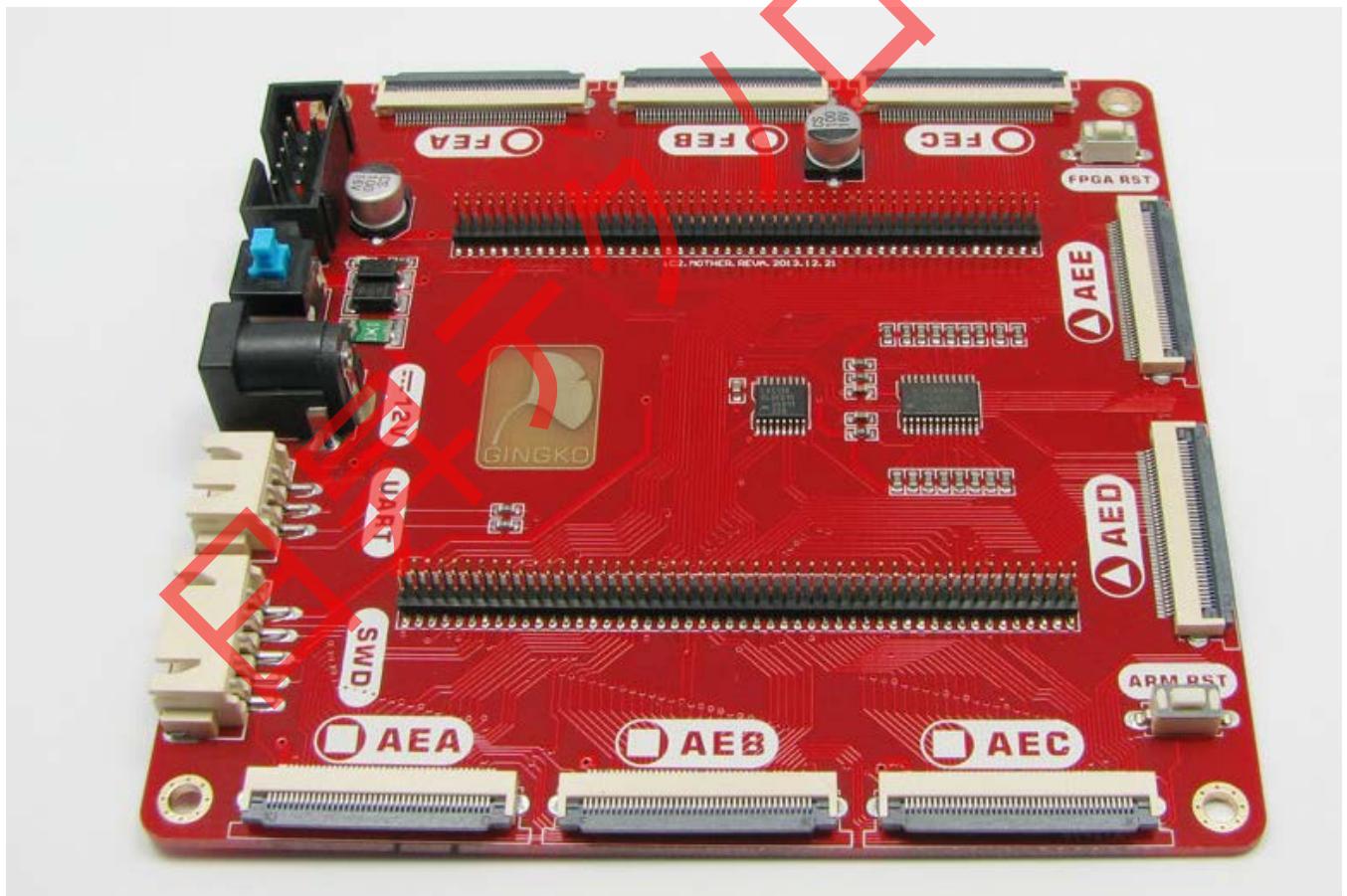

## 16. 実験基板

日常テストとデバッグの便利さを考慮して、icore2に実験基板が設計されている。その機能は下記の通り：

- DC入力ポートポートが搭載されているので、システムに給電でき、入力範囲:5~12V

- FPGA ダウンロードポートが搭載されている。USB Blasterと繋いで、一般的なデバッグの場合、そのインターフェースのご利用が推薦される

- 5pのSWD ダウンロードポートが搭載されていて、JLINK などのデバッカーと接続できる

- FPGA IO拡張ポート、40pin FPCコネクタ × 3(FEA、FEB、FEC) が配置される。具体的なピンの配置は回路図をご参考ください。

- FSMC拡張ポート、40pin FPCコネクタ × 3(AEA、AEB、AEC) が配置される。具体的なピンの配置は回路図をご参考ください。

- STM32 IO拡張ポート、40pin FPCコネクタ × 2(AED、AEE) が配置される。具体的なピンの配置は回路図をご参考ください。

icore2を基板と接続、分解する場合、ピンヘッダーを折り曲げないように十分ご注意ください。周辺から少しづつこじ開けて、こじ開ける時、支点をicore2に搭載された部品(キー、インターフェースなど)に置かないでください。

以上。

日昇テクノロジー