# ZYNQ XC7Z020 開発ボード マニュアル

株式会社日昇テクノロジー

http://www.csun.co.jp

info@csun.co.jp

作成日:2019/6/17

copyright@2019-2020

低価格、高品質が不可能

日昇テクノロジーなら可能にする

### • 修正履歴

| NO | バージョン  | 修正内容 | 修正日       |

|----|--------|------|-----------|

| 1  | Ver1.0 | 新規作成 | 2019/6/17 |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

※ この文書の情報は、文書を改善するため、事前の通知なく変更されることがあります。最新版は弊社ホームページからご参照ください。

Thttps://www.csun.co.jpj

※ (株)日昇テクノロジーの書面による許可のない複製は、いかなる形態においても厳重に禁じられています。

# ソフトウエアバージョンについて

本マニュアルはXilinx公式から提供されたVivado バージョンを使用しています。Xilinx 公式サイトで正しいバージョンをダウンロードしてご利用ください。

### 目次

| _  | 概   | 要                   | 5  |

|----|-----|---------------------|----|

| _  | PC  | B サイズ               | 6  |

| 三  | 電   | 源                   | 8  |

| 四  | ZYI | NQ7000              | 10 |

| 五. | ク   | ロック設定               | 15 |

| 5  | . 1 | PS システムクロックソース      | 15 |

| 5  | . 2 | PL システムクロックソース      | 17 |

| 六  | PS  | 側の外部デバイス            |    |

| 6  | . 1 | QSPI Flash          | 19 |

| 6  | . 2 | DDR3 DRAM           | 21 |

| 6  | . 3 | ギガビットイーサネットインターフェース | 26 |

| 6  | . 4 | USB2. 0             | 31 |

| 6  | . 5 | usb to serial       |    |

| 6  | . 6 | SD カードスロット          | 36 |

| 6  | . 7 | PS PMOD コネクタ        | 39 |

| 6  | . 8 | ユーザーLED             | 40 |

| 6  | . 9 | ユーザーキー              | 41 |

| 七  | PL  | 側の周辺機器              |    |

| 7  | . 1 | HDMI インターフェース       | 43 |

| 7  | . 2 | EEPROM 24LC04       | 45 |

| 7  | . 3 | リアルタイムクロック DS1302   | 46 |

| 7  | . 4 | 拡張ポート 110           | 48 |

| 7  | . 5 | 拡張ポート <b>J11</b>    | 51 |

| 7  | . 6 | <b>ユーザーLED</b>      | 54 |

| 7  | . 7 | ユーザーキー              | 55 |

|    |     |                     |    |

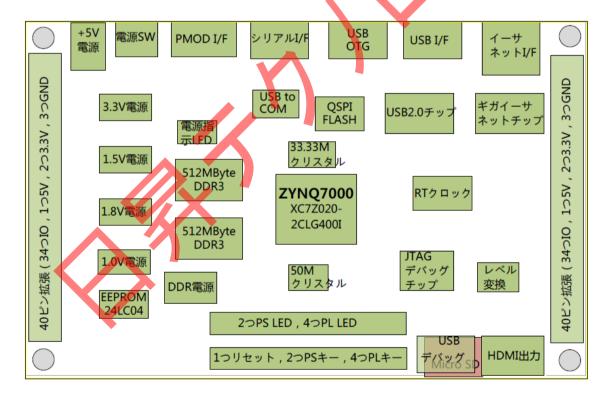

この開発プラットフォーム (型番: AX7020) は XILINX の Zyng7000 SOC チップのソ リューションであり、 ARM+FPGA SOC 技術で2コア ARM Cortex-A9 と FPGA プログラマブ ルロジックを一つのチップに統合している。 Xilinx の Zyng7000 シリーズである XC7Z020-2CLG400I をコアプロセッサとして、ARM と FPGA には各自いろんなハードソース や外部インタフェースがある。本ボードは実用、簡潔に設計し、開発担当者の前期のソフ ト検証に適応するだけでなく、ハードウエアの設計にも便利で、プロジェクト開発期間が 短縮できる。

ZYNQ 開発ボード

#### 一 概要

ZYNQ7000 開発プラットフォーム AX7020 については簡単に紹介する。

この開発ボードは Xilinx 社の Zynq7000 シリーズのチップをしている。型番: XC7Z020-2CLG400I、 400 ピン FBGA パッケージ。ZYNQ7000 チップはプロセッサシステム部分 Processor System (PS) とプログラマブルロジック部分 Programmable Logic (PL) で構成している。 AX7020 開発ボードで、ZYNQ7000 の PS 部分と PL 部分いろんな外部インタフェースとデバイスを搭載されていて、ユーザーにとっては使用及び機能検証しやすくなる。また、開発ボードに Xilinx USB Cable ダウンローダ回路を内蔵しているので、一本の USB ケーブルだけでダウンロードとデバッグを行うことができる。図 1-2 は AX7020 全体システムを示している:

1-2 AX7020 構造概略図

口弁アクノロシーならり配にする

上記図の通り、本開発プラットフォームに含めるインターフェースと機能がある。

- +5V 電源入力、最大 2A まで電流保護

- Xilinx ARM+FPGA チップ Zyng-7000 XC7Z020-2CLG400I

- 2 枚の大容量 4Gbit (合計 8Gbit) の高速 DDR3 SDRAM 搭載、ZYNQ チップデータのキャッシュとして使用、または OS を実行されるメモリとして使用する

- 一枚の 256Mbit QSPI FLASH を搭載、ZYNQ チップのシステムファイル及びユーザーデータを保存するために使用する

- 一つの 10/100M/1000M イーサネット RJ-45 I/F、パソコンや他のデバイスとのイーサネットデータ通信に使用する

- 一つの HDMI 画像ビデオ入出力 I/F、1080P のビデオ画像伝送に使用する

- 一つの高速 USB2.0 HOST I/F、開発ボードとマウス、キーボード、USB メモリなどの外部デバイスとの接続に使用する

- 一つの高速 USB2.0 OTG I/F、PC あるいは USB デバイスとの OTG 通信に使用する

- 一つの USB Uart I/F、PC あるいは外部デバイスとのシリアル通信に使用する

- 一つの RTC リアルタイムクロック、電池ホルダーを搭載、電池の型番は CR1220

- 一枚の IIC インターフェースの EEPROM 24LC04

- 六つの発光ダイオード LED、二つは PSコントロール、四つは PL コントロール

- 七つのキー、一つの CPU リセットギー、こつの PS 制御キー、四つの PL 制御キー

- 33.333Mhz のアクティブ水晶発振器を搭載、PS システムに安定なクロックソースを提供する。そして、PL ロジックに別のクロックを提供するために、一つの 50MHz のアクティブ水晶発振器も搭載

- 2つの40ピンの拡張ポート (2.54MM ピッチ)、ZYNQ の PL 部分の IO の拡張に使用される。このポートは 7 インチ TFT モジュール、カメラモジュール、AD/DA モジュールなどの拡張モジュールと接続できる

- 一つの12ピンの拡張ポート、ZYNQのPSシステム部分のMIOを拡張する

- 一つの USB JTAG ポート、USB ケーブルと開発ボードに搭載される JTAG 回路で ZYNQ システムのデバッグとダウンロードできる

- 一つの MicroSD スロット (開発ボードの裏面)、OS イメージとファイルシステムを保存する

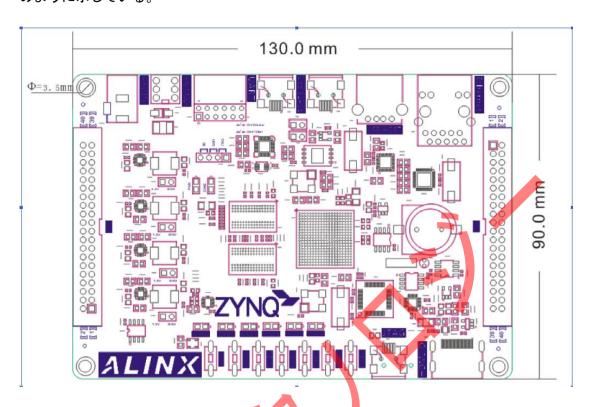

#### ニ PCB サイズ

開発ボードのサイズは 130mm x 90mm で、PCB は八層ボードで設計している。このボードの四つ角にはそれぞれねじ穴があって、開発ボードを固める。穴の直径は 3.5mmで、下図

#### のように示している。

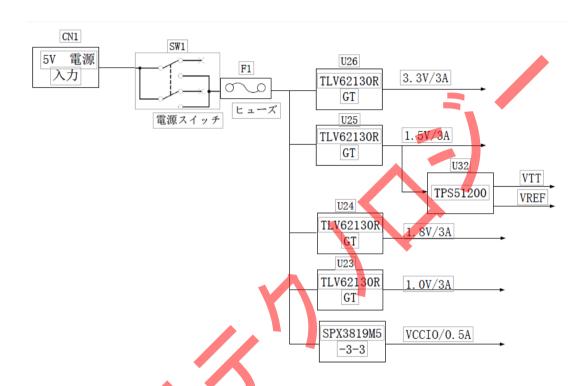

#### 三 電源

電源入力: 開発ボードは給電電圧は DC5V で、開発ボードを損害しないため別の規格の電源 アダプタは使用しないでください。開発ボードの電源部分の設計図は以下のように示して いる:

図3-1 電源インタフェース部分の回路図

開発ボードに 5 v 電圧を提供していて、 4 つの DC/DC 電源チップ TLV62130RGT で + 5 v を +3. 3V, +1. 5V, +1. 8V, +1. 0V の四つの電源に転換されて、それぞれの出力電流は最大 3 A。 -0の LD0 SPX3819M5-3-3 で VCCIO 電源を生じている。VCCIO は主に ZYNQ の BANK35 に対し給電して、ほかの LD0 チップに切り替えることで、BANK35 の IO がそれぞれの電圧標準に合わせる。 1.5V は TI の TPS51200 で DDR 3 が必要となる VTT と VREF 電圧を生じる。それぞれの電源に配置する機能は下表のように示している:

| 電源機能 |

|------|

|------|

| +3. 3V    | ZYNQ VCCIO,イーサネット、シリアルポート、HDMI,RTC,FLASH,      |

|-----------|------------------------------------------------|

|           | EEPROM 及び SD card                              |

| +1.8V     | ZYNQ 補助電圧, ZYNQ PLL, ZYNQ Bank501、VCCIO, イーサネッ |

|           | ►, USB2. 0                                     |

| +1. 0V    | ZYNQ のコア電圧                                     |

| +1.5V     | DDR3, ZYNQ Bank502                             |

| VREF, VTT | DDR3                                           |

| VCCIO     | ZYNQ Bank35                                    |

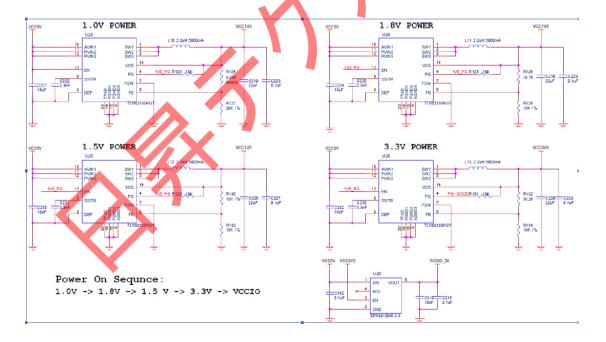

ZYNQ での PS と PL 部分は電源投入に対して順番が要求される。回路設計では ZYQN の電源要求に従って、電源入れ順番は 1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO。図3-2は電源の回路設計図です:

図3-2 開発ボードの電源回路設計図

PCB を設計しているときは八層 PCB で独立の電源層と GND 層を留保したので、開発ボードに安定性の高さを実現する。 PCB ボードで各電源にテストポイントを保留したので、ユーザー

低価格、高品質が不可能? 日昇テクノロジーなら可能にする

はボードでの電圧を確認する時も便利になる。

図 3-3 実物図での電源テストポイント

#### 四 ZYNQ7000

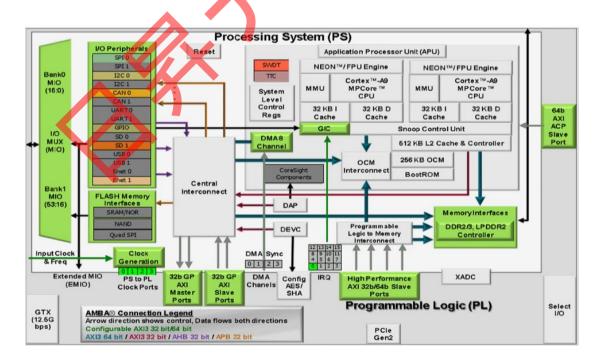

開発ボードでは型番が XC7Z020-2CLG400I という Xilinx 会社の Zynq7000 シリーズのチップを使用している。チップの PS システムには二つ ARM Cortex → A9 プロセッサ、AMBA®互連、内部メモリ、外部メモリインタフェース及び外部デバイスがある。これらの外部デバイスには USB バスインターフェース、イーサネットインターフェース、SD/SDIO インターフェース、CANバスインターフェース、UART インターフェース、GPIOなどを含む。PS は電源入れ後またはリセット後で独立して実行できる。ZYNQ7000 チップの全体ブロックは図 4 − 1 のように示している:

#### 図 4 - 1 ZYNQ 7 O O O チップの全体ブロック図

PS システム部分の主なパラメータは以下とおりです:

- -ARM 2コア CortexA9 のプロセッサ

- -各 CPU に 32KB の一級コマンドとデータキャッシュ、二つの CPU が 512KB の二級キャッシュを共有

- -boot ROM 内蔵、 256KB RAM 内蔵

- -外部メモリインターフェース、16/32 bit DDR2、DDR3 のインターフェースをサポート

- -二つのギガビットネットワークカードをサポート:分散一集約 DMA、GMII、RGMII、SGMII インターフェース

- -二つの USB2. 0 OTG インターフェース、それぞれ 1 2 までのノードをサポート

- -二つの CAN2. OB バスインターフェース

- -二つの SD カード、SDIO、MMC Compatible controller

- -二つの SPI、二つの UARTs、二つの I2C インターフェース;

- -4組 32bit GPIO、54 (32+22) はPS システムのIOとする、64はPLに接続

- -PS 内部および PS と PL 間を広帯域接続

- PL ロジック部分のパラメータは以下のとおりです:

- -ロジックユニットLogic Cells:85K

- -ルックアップテーブル LUTs: 53,200

- -トリガー(flip-flops): 106,400

- 乗算器 18x25MACCs: 220

-Block RAM: 4.9 Mb

-二つの AD コンバーターは内蔵電圧、温度感応、及び最大 17 の外部差分入力チャンネルを 測定できる、1MBPS。

XC7Z020-2CLG400I チップは BGA パッケージで、400ピンがあって、それぞれのピン間隔は 0.8mm。ちなみに、BGA でパッケージされたチップを使用した後、BGA ピンの名称は「英語+数字」という形式になる。たとえば、E3、G3。これは BGA のピンと代表している。

図 4 - 2 XC7Z020 チップの実物図

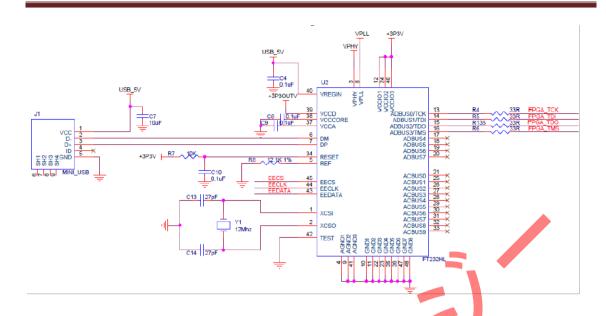

#### 1) JTAG インターフェース

AX7020 開発ボードに JTAG のダウンロードデバッグ回路を統合しているので、ユーザーは別の XILINX のダウンローダを用意する必要がない。一本の USB ラインだけで JTAG のデバッグインターフェースを PC と接続して ZYBQ をデバッグができる。AX7020 開発ボードでは FIDI の USB ブリッジチップ FT232HL で PC の USB と ZYNQ の JTAG デバッグ信号 TCK、TDO、TMS、TDI とのデータ通信を実現できる。図 4-3 は開発ボードにある JTAG インターフェースの回路図です:

図4-3 JTAG インターフェース部分

図4-4JTAG インターフェースの実物図

#### 2) FPGA 給電システム

ZYNQ チップの電源は PS システム部分と PL ロジック部分に分かれている。この二つの電源は別々働いている。PS システム部分の電源と PL ロジック部分の電源は電源入れ順番があるので、もし順番に従わないと ARM システムと FPGA システム、両方も正常に働けなくなる可能性もある。

PS 部分の電源には VCCPINT、VCCPAUX、VCCPLL 及び PS VCCO がある。 VCCPINT は PS コア給電ピンとして 1.0V と接続する。 VCCPAUX は PS システム補助給電ピンとして 1.8V と接続する。 VCCPLL は PS の内部クロックである PLL の電源給電ピンとして 1.8V と接続する。 PS VCCO は BANK の電圧で、

VCCO\_MIOO, VCCO\_MIO1 及び VCCO\_DDR を含む。外部デバイスによって、接続する電源も違う。AX7020 開発ボードでは VCC\_MIOO は 3.3V と接続して、CCO\_MIO1 は 1.8V と接続して、VCCO\_DDR は 1.5V と接続する。PS システムの電源入れ順番は VCCPINT 給電一>VCCPAUX と VCCPLL—>PS VCCO にしなければならない。電源切れのときの順序が逆になる。

PL 部分の電源には VCCINT, VCCBRAM, VCCAUX 及び VCCO がある。VCCPINT は FPGA コア給電ピンとして 1.0V と接続し、VCCBRAM は FPGA Block RAM の給電ピンとして 1.0V と接続し、VCCAUX は FPGA の補助給電ピンとして 1.8V と接続し、VCCO は PL の各 BANK の電圧で、BANK13, BANK34 及び BANK35 を含む。AX7020 開発ボードで BANK の電圧は 3.3V と接続する。PS システムの電源入れ順番は VCCPINT 給電一>VCCBRAM—>VCCAUX—>VCCO にしなければならない。もし VCCINT が VCCBRAM と同じ電圧であれば、同時に電源入れることができる。電源切れのときの順序が逆になる。

#### 3) ZYNQ 起動設定

AX7020 開発プラットフォームは JTAG デバッグモード、QSPI FLASH 及び SD カード起動モ

日屋テクノロジーから可能にする

ードという三つの起動モードをサポート。ZYNQ702 チップが電源入れた後、MIO ポートに反応するレベルを検測してどんな起動モードにするかを決める。ユーザーはコアボードにある J13 のジャンパーにより異なる起動モードを選択できる。J13 起動モードの設定は下図 4 ー1 のように示している。

| J13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ジャンパーキャップ位置  | 起動モード      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|

| I AS R86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 左の二つのピンを接続   | SD Card    |

| \(\frac{1}{2}\) \(\frac{1}\) \(\frac{1}{2}\) \(\frac{1}2\) \(\frac{1}2\) \(\frac{1}2\) \(\frac{1}2\) \( | 真ん中の二つのピンを接続 | QSPI FLASH |

| J13 R16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 右の二つのピンを接続   | JTAG       |

図 4-1 J13 起動モード設定

#### 五 クロック設定

AX7020 開発ボードは PS システムと PL ロジック部分に別々にアクティブクロックを提供して、PS システムと PL ロジック部分は独立で働ける。

#### 5.1 PSシステムクロックソース

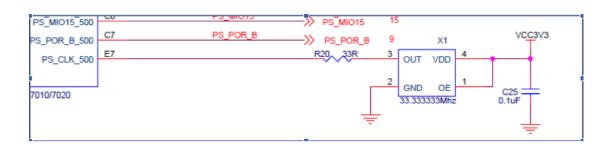

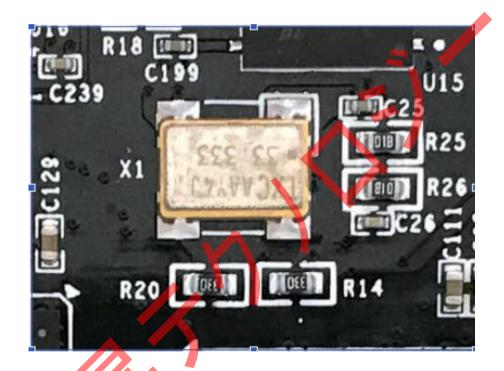

ZYNQ チップは開発ボードでの X1 水晶発振器で PS 部分に 33.333MHZ のクロック入力を提供 している。クロック入力を ZYNQ チップの BANK500 の PS\_CLK\_500 のピンに接続する。回路 図は図 5-1 のように示している:

図 5-1 PS 部分のアクティブ水晶発振器

図 5-2 33.333Mhz アクティブ水晶発振器の実物図

### クロックピン割り当て:

| 信号名        | ZYNQ ピン |  |

|------------|---------|--|

| PS_CLK_500 | E7      |  |

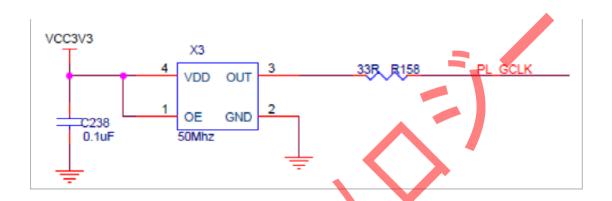

#### 5.2 PL システムクロックソース

AX7020 開発ボードでは 50MHz の PL システムクロックソースを提供して 3.3V 給電している。 水晶発振器出力は FPGA のグローバルクロック (MRCC) と接続して、GCLK は FPGA でのロジ ック回路を駆動するに用いられる。このクロックソースの回路図は図5-3のように示して いる。

図 5-3 PL システムクロックソース

図 5-4 50Mhz アクティブ水晶発振器の実物図

PL クロックピン割り当て:

|      | Her 18-11 |    |         | .,           | -   |

|------|-----------|----|---------|--------------|-----|

|      |           |    |         |              |     |

| 18.4 | 410       | *2 | A TITLE | <b>W</b> 17. | + 2 |

| 信号名     | ZYNQ ピン |

|---------|---------|

| PL_GCLK | U18     |

#### 六 PS側の外部デバイス

ZYNQ は ARM システムの PS 部分と FPGA ロジックの PL 部分から構成されていて、開発ボードでは一部の外部デバイスは PS の IO と接続して、一部は PL の IO と接続する。

まず、PS 部分と接続する外部デバイスを紹介する。

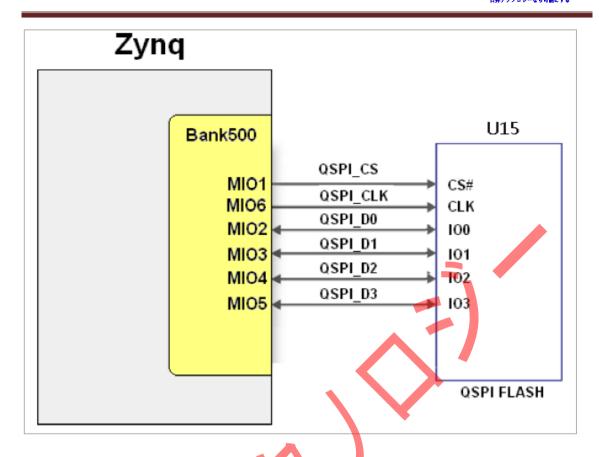

#### 6.1 QSPI Flash

開発ボードに型番が W25Q256 の 256Mbit の Quad-SPI FLASH チップを搭載して 3.3VCMOS の電圧標準に従う。 QSPI FLASH は不揮発性があるので、使用している場合、システムの起動デバイスとして、システムの起動イメージを保存する。これらのイメージは主に FPGA のbit ファイル、ARM のアプリコード及びその他のユーザーデータファイルを含む。QSPI FLASHの具体的な型番と関連パラメータは表 6-1 をご参照ください:

| ビット数 | チップタイプ  | 容量       | メーカー    |

|------|---------|----------|---------|

| U6   | W25Q256 | 32M Byte | Winbond |

表 6-1 QSPI Flash の型番とパラメータ

QSPI FLASH は ZYNQ チップの PS 部分 BANK500 の GPIO ポートと接続する。システム設計ではこれらの PS 側の GPIO ポートを QSPI FLASH インタフェースに配置する必要がある。図 6 -1 は QSPI Flash がハードウエアの接続図。

図 6-1 QSPI Flash 接続図

## 配置チップピン割り当て:

| 信号名      | ZYNQ ピン名    | ZYNQ ピン番号  |

|----------|-------------|------------|

| QSPI_CLK | PS_MIO6_500 | <b>A</b> 5 |

| QSPL CS  | PS_MI01_500 | A7         |

| QSPI DO  | PS_MIO2_500 | B8         |

| QSPI_D1  | PS_MI03_500 | D6         |

| QSPI_D2  | PS_MIO4_500 | В7         |

| QSPI_D3  | PS_MI05_500 | A6         |

#### 6.2 DDR3 DRAM

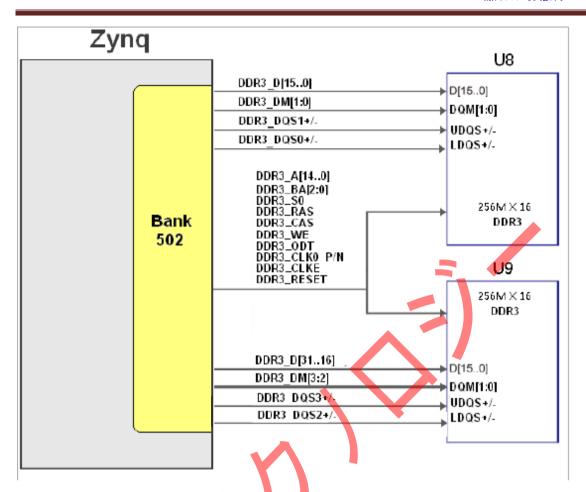

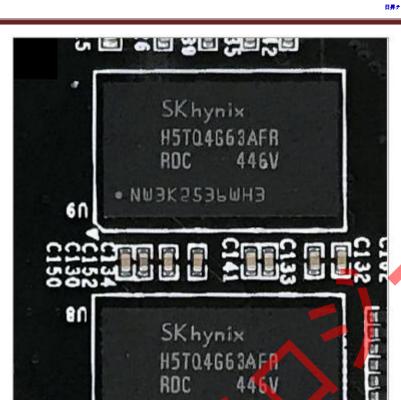

AX7020 開発ボードに型番が H5TQ4G63AFR-PBC (MT41J256M16HA-125 とコンパチ) の SK hvnix の 4Gbit (512MB) の DDR 3 チップを二つ(合計 8Gbit)を搭載。DDR のバス幅は合計 32bit。 DDR3 SDRAM の処理速度は最大 533MHz (データレートが 1066Mbps)に達す。DDR3 ストレージ システム は ZYNQ 処理システム (PS) の BANK 502 のメモリインターフェースと接続。DDR3 SDRAM の具体的な配置は下表 6-1 のように示す:

| ビット数   | チップタイプ          | 容量           | メーカー   |

|--------|-----------------|--------------|--------|

| U8, U9 | H5TQ4G63AFR-PBC | 256M x 16bit | micron |

表 6-1 DDR3 SDRAM 配置

DDR3 のハードウエア設計については信号の完全性が必須。回路と PCB を設計しているとき はマッチング抵抗/終端抵抗、配線抵抗制御、配線等長制御などをちゃんと考えて、DDR3は 高速且つ安定で動くことと保証する。DDR3 DRAM のハードウェア接続図は図 6-2 のように 示す:

日昇テクノロジーなら可能にする

図 6-2 DDR3 DRAM 回路図部分

図 6-3 DDR3 DRAM 実物図

NM3K523PMH3

### DDR3 DRAM ピン割り当て

| 信号名         | ZYNQ ピン名          | ZYNQ ピン番号 |

|-------------|-------------------|-----------|

| DDR3 DQS0 P | PS_DDR_DQS_P0_502 | C2        |

| DDR3_DQS0_N | PS_DDR_DQS_NO_502 | B2        |

| DDR3_DQS1_P | PS_DDR_DQS_P1_502 | G2        |

| DDR3_DQS1_N | PS_DDR_DQS_N1_502 | F2        |

| DDR3_DQS2_P | PS_DDR_DQS_P2_502 | R2        |

| DDR3_DQS2_N | PS_DDR_DQS_N2_502 | T2        |

| DDR3_DQS3_P | PS_DDR_DQS_P3_502 | W5        |

日昇テクノロジーなら可能にする

| DDR3_DQS4_N  | PS_DDR_DQS_N3_502 | W4 |

|--------------|-------------------|----|

| DDR3_DQ[0]   | PS_DDR_DQ0_502    | C3 |

| DDR3_DQ [1]  | PS_DDR_DQ1_502    | B3 |

| DDR3_DQ [2]  | PS_DDR_DQ2_502    | A2 |

| DDR3_DQ [3]  | PS_DDR_DQ3_502    | A4 |

| DDR3_DQ [4]  | PS_DDR_DQ4_502    | D3 |

| DDR3_DQ [5]  | PS_DDR_DQ5_502    | D1 |

| DDR3 DQ [6]  | PS_DDR_DQ6_502    | C1 |

| DDR3_DQ [7]  | PS_DDR_DQ7_502    | E1 |

| DDR3_DQ [8]  | PS_DDR_DQ8_502    | E2 |

| DDR3_DQ [9]  | PS_DDR_DQ9_502    | E3 |

|              |                   |    |

| DDR3_DQ [10] | PS_DDR_DQ10_502   | G3 |

| DDR3_DQ [11] | PS_DDR_DQ11_502   | Н3 |

| DDR3_DQ [12] | PS_DDR_DQ12_502   | J3 |

| DDR3_DQ [13] | PS_DDR_DQ13_502   | H2 |

| DDR3 DQ [14] | PS_DDR_DQ14_502   | H1 |

| DDR3_DQ [15] | PS_DDR_DQ15_502   | J1 |

| DDR3_D0 [16] | PS_DDR_DQ16_502   | P1 |

| DDR3_DQ [17] | PS_DDR_DQ17_502   | P3 |

| DDR3_DQ [18] | PS_DDR_DQ18_502   | R3 |

| DDR3_DQ [19] | PS_DDR_DQ19_502   | R1 |

| DDR3_DQ [20] | PS_DDR_DQ20_502   | T4 |

| DDR3_DQ [21] | PS_DDR_DQ21_502   | U4 |

日昇テクノロジーなら可能にする

| DDR3_DQ [22] | PS_DDR_DQ22_502 | U2         |

|--------------|-----------------|------------|

| DDR3_DQ [23] | PS_DDR_DQ23_502 | U3         |

| DDR3_DQ [24] | PS_DDR_DQ24_502 | V1         |

| DDR3_DQ [25] | PS_DDR_DQ25_502 | Y3         |

| DDR3_DQ [26] | PS_DDR_DQ26_502 | W1         |

| DDR3_DQ [27] | PS_DDR_DQ27_502 | Y4         |

| DDR3_DQ [28] | PS_DDR_DQ28_502 | Y2         |

| DDR3_DQ [29] | PS_DDR_DQ29_502 | W3         |

| DDR3_DQ [30] | PS_DDR_DQ30_502 | V2         |

| DDR3_DQ [31] | PS_DDR_DQ31_502 | V3         |

| DDR3_DM0     | PS_DDR_DM0_502  | A1         |

| DDR3_DM1     | PS_DDR_DM1_502  | F1         |

|              |                 |            |

| DDR3_DM2     | PS_DDR_DM2_502  | T1         |

| DDR3_DM3     | PS_DDR_DM3_502  | Y1         |

| DDR3_A[0]    | PS_DDR_A0_502   | N2         |

| DDR3_A[1]    | PS_DDR_A1_502   | К2         |

| DDR3_A[2]    | PS_DDR_A2_502   | M3         |

| DDR3_A[3]    | PS_DDR_A3_502   | K3         |

| DDR3_A[4]    | PS_DDR_A4_502   | M4         |

| DDR3_A[5]    | PS_DDR_A5_502   | L1         |

| DDR3_A[6]    | PS_DDR_A6_502   | L4         |

| DDR3_A[7]    | PS_DDR_A7_502   | K4         |

| DDR3_A[8]    | PS_DDR_A8_502   | <b>K</b> 1 |

| DDR3_A[9]  | PS_DDR_A9_502     | J4 |

|------------|-------------------|----|

| DDR3_A[10] | PS_DDR_A10_502    | F5 |

| DDR3_A[11] | PS_DDR_A11_502    | G4 |

| DDR3_A[12] | PS_DDR_A12_502    | E4 |

| DDR3_A[13] | PS_DDR_A13_502    | D4 |

| DDR3_A[14] | PS_DDR_A14_502    | F4 |

| DDR3_BA[0] | PS_DDR_BAO_502    | L5 |

| DDR3_BA[1] | PS_DDR_BA1_502    | R4 |

| DDR3_BA[2] | PS_DDR_BA2_502    | J5 |

| DDR3_S0    | PS_DDR_CS_B_502   | N1 |

| DDR3_RAS   | PS_DDR_RAS_B_502  | P4 |

| DDR3_CAS   | PS_DDR_CAS_B_502  | P5 |

| DDR3 WE    | PS_DDR_WE_B_502   | M5 |

| DDR3_ODT   | PS_DDR_ODT_502    | N5 |

| DDR3_RESET | PS_DDR_DRST_B_502 | B4 |

| DDR3_CLK_P | PS_DDR_CKP_502    | L2 |

| DDR3_CLK_N | PS_DDR_CKN_502    | M2 |

| DDR3_CKE   | PS_DDR_CKE_502    | N3 |

#### 6.3 ギガビットイーサネットインターフェース

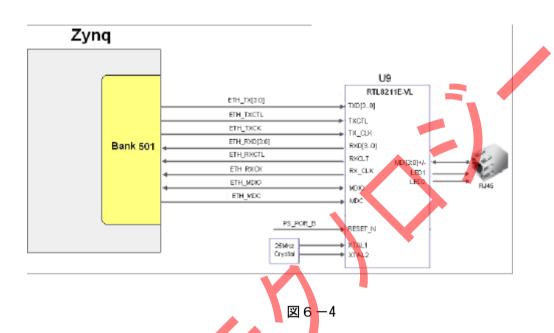

AX7020 開発ボードは Realtek RTL8211E-VL イーサネット PHY チップでネット通信サービス を実現。

イーサネット PHY チップは ZYNQ の PS 側 BANK501 の GPIO インターフェースに接続。 RTL8211E-VL チップは 10/100/1000 Mbps のインターネット伝送レートを支持して、 RGMII インターフェースで Zynq7000 PS システムの MAC 層とのデータ通信を行う。RTL8211E-VL は MDI/MDX アダプティブ、各スピードのアダプティブ、Master/Slave アダプティブ、MDIO バスが PHY のレジスター管理を行うなどを支持する。

RTL8211E-VL が電源入れると、特定の I0 のレベル状態を検測して自体の作業モードを確認する。表 6-2 は GPHY チップが電源入れた後設定したデフォルト情報。

| ピンの配置      | 説明                          | 配置値               |

|------------|-----------------------------|-------------------|

| PHYAD[2:0] | MDIO/MDC モードの PHY アドレス      | PHY Address が 001 |

| SELRGV     | RGMII 1.8V あるいは 1.5V のレベル選択 | 1. 8V             |

| AN[1:0]    | オートネゴシエーション配置               | (10/100/1000M)アダプ |

|            |                             | ティブ               |

| RX Delay   | RX クロック 2ns 遅延              | 遅延                |

| TX Delay   | TX クロック 2ns 遅延              | 遅延                |

表 6-2 PHY チップデフォルト配置値

ギガビットイーサネットに接続すると、FPGA と PHY チップ RTL8211E-VL とのデータ通信は RGMII バスで実現する。伝送クロックは 125Mhz で、データはクロックの立ち上がりエッジ と立ち下がりエッジでサンプリングする。

100M イーサネットに接続すると、FPGA と PHY チップ RTL8211E-VL とのデータ通信は RMII バスで実現します。伝送クロックは 25Mhz で、データはクロックの立ち上がりエッジと立ち下がりエッジでサンプリングします。

図 6-4 は ZYNQ とイーサネット PHY チップとの連続概略図:

図 6-5 はイーサネット PHY チップの実物図:

図 6-5

### イーサネットのピン配置は以下のように示しています:

| 信号名       | ZYNQ ピン名     | ZYNQ ピン番号 | 備考             |

|-----------|--------------|-----------|----------------|

| ETH_GCLK  | PS_MI016_501 | A19       | RGMII がクロックを送信 |

| ETH_TXD0  | PS_MI017_501 | E14       | データ bit O を送信  |

| ETH_TXD1  | PS_MI018_501 | B18       | データ bit1 を送信   |

| ETH_TXD2  | PS_MI019_501 | D10       | データ bjt2 を送信   |

| ETH_TXD3  | PS_MI020_501 | A17       | データ bit を送信    |

| ETH_TXCTL | PS_MI021_501 | F14       | 作業信号を送信        |

| ETH_RXCK  | PS_MI022_501 | B17       | RGMII がクロックを受信 |

| ETH_RXD0  | PS_M1023_501 | D11       | データ bit O を受信  |

| ETH_RXD1  | PS_MI024_501 | A16       | データ bit1 を受信   |

| ETH_RXD2  | PS_MI025_501 | F15       | データ bit2 を受信   |

| ETH_RXD3  | PS_MI026_501 | A15       | データ bit3 を受信   |

| ETH_RXCTL | PS_MI027_501 | D13       | 有効信号のデータを受信    |

低価格、高品質が不可能

|異チクノロジーなら可能にする

| ETH_MDC  | PS_MI052_501 | C10 | MDIO 管理クロック |

|----------|--------------|-----|-------------|

| ETH_MDIO | PS_MI053_501 | C11 | MDIO 管理データ  |

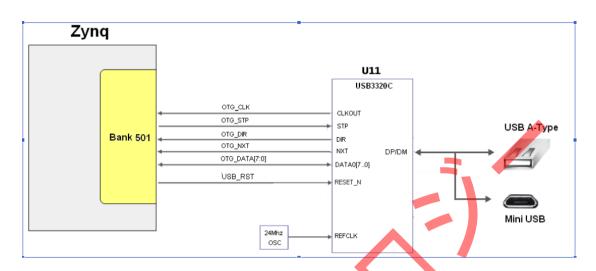

#### 6.4 USB2.0

AX7020 には、1.8V、高速的に ULPI 標準インターフェースを支持する USB3320C-EZK の USB2.0 トランシーバーを搭載。 ZYNQ の USB バスは USB3320C-EZK トランシーバーと接続して高速的に USB2.0 Host と Slave モードとのデータ通信を実現する。 USB3320C の USB のデータと制御信号は ZYNQ チップの PS 側の BANK501 の IO インターフェースと接続して、一つの 24MHz の水晶発振器は USB3320C にシステムクロックを提供する。

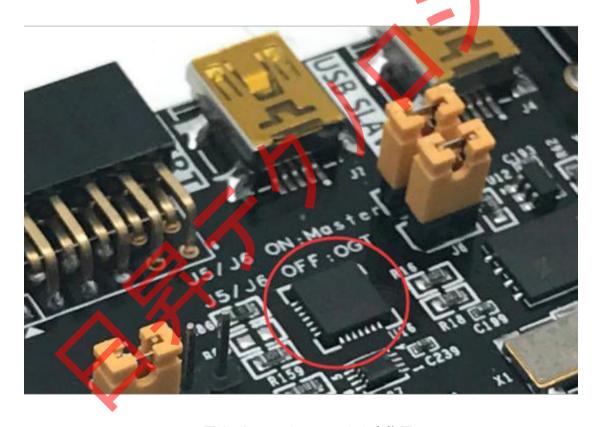

開発ボードはユーザーに二つの USB インターフェースを提供していて、一つは Host USB インターフェース、もう一つは Slave USB インターフェース。それに、一つはフラット USB インターフェース (USB Type A) 、もう一つはマイクロ USB インターフェース (Micro USB) でユーザーが異なる USB 外部デバイスとの接続を便利にする。ユーザーは開発ボードでの J5, J6 のジャンパーで Host と Slave との切り替えを実現できる。図 6-3 はモードの切り替え説明です:

| J5, J6 ステータス USB <b>モ</b> ード         | 説明                                                       |

|--------------------------------------|----------------------------------------------------------|

| J5とJ6はジャンパーキャッ Host モード<br>プを取り付け    | 開発ボードをマスターデバイスにし、USB インターフェースはマウス、キーボード、USB などの外部デバイスと接続 |

| J5とJ6はジャンパーキャッ Slave モード<br>プを取り付けない | 開発ボードはスレーブデバイスとし、USB インターフェイスは PC と接続                    |

図 6-3 モードの切り替え説明

日展テクノロジーかる可能にする

ZYNQ プロセッサと USB33200-EZK チップとの接続概略図は図 6-6 のように示す:

図 6-6 Zynq7000 と USB チップとの接続概略図

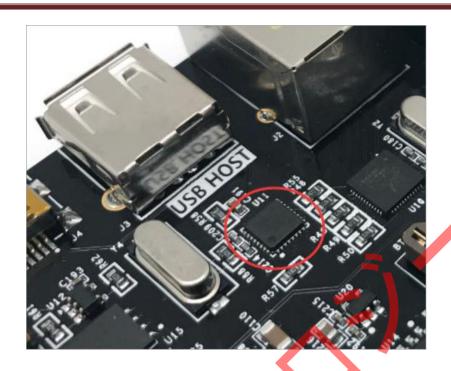

図 6-7 は USB2. 0 部分の実物図です。UI11 は USB3320C、J3 为 Host USB のインターフェースで、J4 は Slave USB のインターフェース。ジャンパーキャップの J5 と J6 は Host と Slave モードを選択するに用いられる。

図 6-7 USB2.0 部分の実物図

#### USB2.0 ピンの割り当て:

| 信号名       | ZYNQ ピン名      | ZYNQ ピン番号 | 備考           |

|-----------|---------------|-----------|--------------|

| OTG_DATA4 | PS_MI 028_501 | C16       | USB データ Bit4 |

| OTG_DIR   | PS_MI 029_501 | C13       | USB データ方向信号  |

| OTG_STP   | PS_MI030_501  | C15       | USB 停止信号     |

| OTG_NXT   | PS_MI031_501  | E16       | USB 次のデータ信号  |

| OTG_DATAO | PS_MI032_501  | A14       | USB データ BitO |

| OTG_DATA1 | PS_MI033_501  | D15       | USB データ Bit1 |

低価格、高品質が不可能

日見テクノロジーかる可能にす

| OTG_DATA2  | PS_MI034_501 | A12 | USB データ Bit2 |

|------------|--------------|-----|--------------|

| OTG_DATA3  | PS_MI035_501 | F12 | USB データ Bit3 |

| OTG_CLK    | PS_MI036_501 | A11 | USB クロック信号   |

| OTG_DATA5  | PS_MI037_501 | A10 | USB データ Bit5 |

| OTG_DATA6  | PS_MI038_501 | E13 | USB データ Bit6 |

| OTG_DATA7  | PS_MI039_501 | C18 | USB データ Bit7 |

| OTG_RESETN | PS_MI046_501 | D16 | USB リセット信号   |

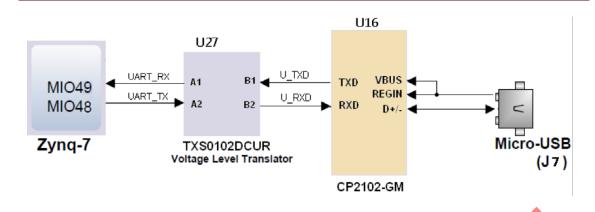

#### 6.5 usb to serial

AX7020 開発ボードでは Silicon Labs CP2102GM の usb to UART チップを利用して、USB インターフェースが Micro USB インターフェースを搭載し、一本の Micro USB ケーブルで PC と接続してシリアル通信ができる。

UART の TX/RX 信号が ZYNQ EPP の PS BANK501 の信号と接続する。当 BANK の VCCMIO は 1.8V に設定されているが、CP2102GM のデータレベルは 3.3V で、

ここは TXS0102DCUR レベル転換チップで接続する。CP2102GM と ZYNQ を接続している接続図は図 6-8 のように示す:

図 6-8 CP2102GM 接続図

図 6-9 usb to serial 実物図

#### ZYNQ シリアルピンの割り当て:

| 信号名 | ZYNQ ピン名 | ZYNQ ピン番号 | 備考 |

|-----|----------|-----------|----|

|-----|----------|-----------|----|

低価格、高品質が不可能

日昇テクノロジーなら可能にする

| UART_TX | PS_MI048_501 | B12 | Uart データ出力 |

|---------|--------------|-----|------------|

| UART_RX | PS_MI049_501 | C12 | Uart データ入力 |

Silicon Labs はホスト PC に仮想 COM ポート (VCP) ドライバを提供している。これらのドライバは CP2102GM USB-UART のようなブリッジ装置がアプリケーションに COM ポートとして表示されることをサポートする。PC と AX7020 開発ボードとの通信をする前に、VCP デバイスドライバはインストールする必要。

#### 6.6 SD カードスロット

AX7020 開発ボードには Micro の SD カードインターフェースを搭載。このインターフェース を通じて SD カードのメモリをアクセスできる。メモリでは ZYNQ チップの B00T プログラム や Linux OS コア、ファイルシステムやその他のデータファイルを保存に利用できる。

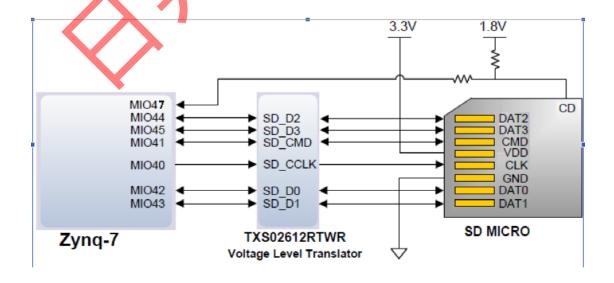

SDIO 信号は ZYNQ の PS BANK501 の IO 信号と接続する。当 BANK の VCCMIO は 1.8V で、SD カードのデータレベルが 3.3V なので、TXSO2612 レベルコンバーターで接続する。Zynq7000 PS と SD カードコネクタの回路図は図 6-10 のように示す:

# 図 6-10 SD カードの接続図

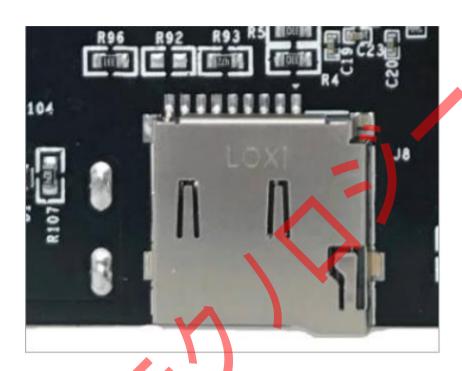

SD カードスロットには開発ボードの裏側にある。図 6-11 は SD カードスロットの実物図で す:

図 6-11 SD カードスロットの実物図

SD カードスロットピンの割り当て

| 信号名    | ZYNQ ピン名 | ZYNQ ピン番号 | 備考           |

|--------|----------|-----------|--------------|

| SD_CLK | PS_MI040 | D14       | SD クロック信号    |

| SD_CMD | PS_MI041 | C17       | SD コマンド信号    |

| SD_D0  | PS_MI042 | E12       | SD データ DataO |

#

| best best life at | had been better at 1 and 100 |

|-------------------|------------------------------|

|                   |                              |

|                   |                              |

|                   |                              |

| SD_D1 | PS_MI043 | A9  | SD データ Data1 |

|-------|----------|-----|--------------|

| SD_D2 | PS_MI044 | F13 | SD データ Data2 |

| SD_D3 | PS_MI045 | B15 | SD データ Data3 |

| SD_CD | PS_MI047 | B14 | SD カード差し込み信号 |

保備格、高品質が不可能

## 6.7 PS PMOD コネクタ

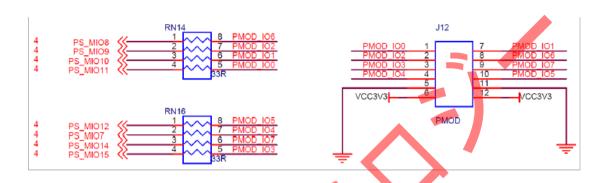

AX7020 開発ボードは 12 ピン 2.54mmピッチの PMOD インターフェース (J12) を保留して、PS BANK500 の I0 と外部モジュールあるいは回路を接続するに用いられる。BANK500 の I0 は 3.3V 標準なので、接続する外部デバイスと回路の信号も 3.3V のレベルが必要。PMOD コネクタの回路図は下図のように示す:

図 6-12 PMOD コネクタ回路図

図 6-13 PS PMOD コネクタの実物図

PS PMOD コネクタのピン割り当て:

| PMOD ピン | 信号名      | ZYNQピン名      | ZYNQ ピン番号 |

|---------|----------|--------------|-----------|

| PIN1    | PMOD_IO0 | PS_MIO11_500 | C6        |

| PIN2    | PMOD_IO2 | PS_MIO9_500  | B5        |

| PIN3    | PMOD_IO3 | PS_MIO15_500 | C8        |

| PIN4    | PMOD_IO4 | PS_MIO7_500  | D8        |

| PIN5    | GND      | -            | -         |

| PIN6    | +3.3V    | -            | -         |

| PIN7    | PMOD_IO1 | PS_MIO10_500 | E9        |

| PIN8    | PMOD_IO6 | PS_MIO8_500  | D5        |

| PIN9    | PMOD_IO7 | PS_MIO14_500 | C5        |

| PIN10   | PMOD_IO5 | PS_MIO12_500 | D9        |

| PIN11   | GND      | -            | -         |

| PIN12   | +3.3V    | -            | -         |

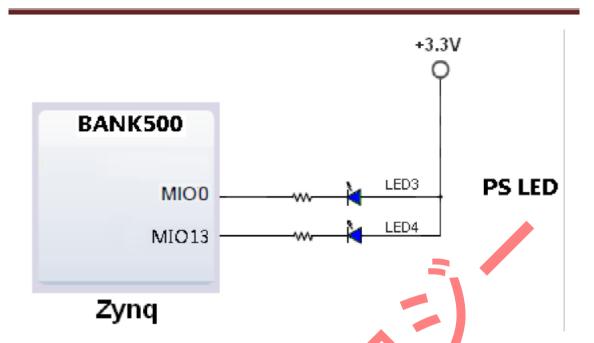

### 6.8 ユーザーLED

AX7020 開発ボードで、PS 部分の BANK500 IO にこつの LED 発光ダイオードを接続している。 これを使ってデバッグに利用できる。BANK500 IO 電圧が高い場合、LED が消灯する。BANK500 IO 電圧が低い場合、点灯する。ZYNQ BANK500 IO と LED を接続している図は以下のように 示す:

図 6-14 ZYNQ BANK500 IO とLED の接続図

図 6-15 PS の LED の実物図

# PS LEDランプのピン割り当て:

| 信号名       | ZYNQ ピン名     | <b>ZYNQ</b> ピン番号 | 備考         |

|-----------|--------------|------------------|------------|

| MIO0_LED  | PS_MIO0_500  | E6               | PS LED1ランプ |

| MIO13_LED | PS_MIO13_500 | E8               | PS LED2ランプ |

# 6.9 ユーザーキー

AX7020 開発ボードで、PS 部分の BANK501 IO に二つのユーザーキーと接続している。ユー

日屋テクノロジーから可能にす

ザーはこのキーを通じて入力信号と割り込みトリガをテストできる。設計に基づいて、キーを押下する場合は ZYNQ BANK501 IO に出力する電圧が低いレベルで、逆に、信号が高いレベルである。ZYNQ BANK501 IO とキーを接続する図は図 6-16 のように示す:

図 6-16 Zynq-7000 とキーとの接続図

図 6-17 PS のキーの実物図

PS KEY のピン割り当て:

| 信号名      | <b>ZYNQ</b> ピン名 | ZYNQピン番号 | 備考           |

|----------|-----------------|----------|--------------|

| MIO_KEY1 | PS_MIO50_501    | B13      | PSユーザーキーKEY1 |

| MIO_KEY2 | PS_MIO51_501    | B9       | PSユーザーキーKEY2 |

### 七 PL側の周辺機器

PL 部分(FPGA ロジック部分)と接続する外部デバイスインタフェースを紹介する。

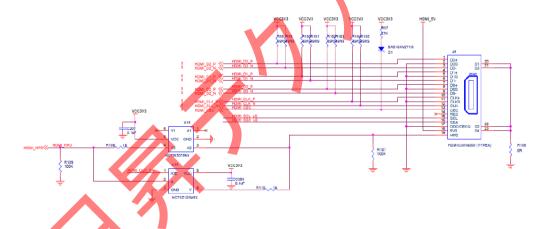

### 7.1 HDMI インターフェース

HDMI とは高解像度マルチメディアインターフェイス。AX7020 開発ボードで、FPGA の差分 IO で HDMI インターフェースの差分信号とクロックに接続して、FPGA 内部で HMDI 信号の差分がパラレルに転換してコーデックする。DMI デジタルビデオ入出力の伝送ソリューションを実現、最大 1080P @ 60Hz の入出力をサポートする。

HDMI の信号は ZYNQ の PL 部分の BANK34 に接続する。図 7-1 は HDMI の設計の回路図。 開発ボードは HDMI のモニター(HDMI IN)とするとき、HDMI 信号は入力、HPD (hot plug detect) 信号は出力です。開発ボードは HDMI のマスターデバイス(HDMI OUT)の際は逆。

図 7-1 HDMI 設計の回路図

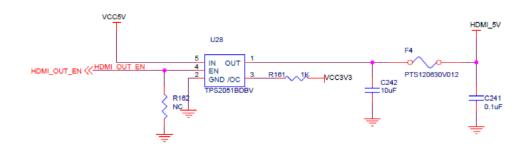

開発ボードは HDMI のマスターデバイスとする場合は、HDMI モニターに+5V の電源を提供する必要がある。電源出力制御回路は図 7-2 のように示す:

図 7-2 HDMI 5V 出力回路

なお、HMDI マスターデバイスは IIC バスで HDMI モニターの EDID デバイスの情報を読み取る。FPGA のピンレベルは 3.3V で、HDMI のレベルは+5V です。ここはレベル転換チップ GTL2002D で接続する。IIC の転換回路は図7-3のように示す:

図 7-3 GTL2002D レベル転換回路

図 7-4 HDMI インターフェースの実物図

HDMI インターフェースのピン割り当て:

| 信号名         | ZYNQ ピン名           | ZYNQピン番号 | 備考                       |

|-------------|--------------------|----------|--------------------------|

| HDMI_CLK_P  | IO_L13P_T2_MRCC_34 | N18      | HDMIクロック信号正              |

| HDMI_CLK_N  | IO_L13N_T2_MRCC_34 | P19      | HDMIクロック信 <del>号</del> 負 |

| HDMI_D0_P   | IO_L16P_T2_34      | V20      | HDMIデータ0正                |

| HDMI_D0_N   | IO_L16N_T2_34      | W20      | HDMIデータ0負                |

| HDMI_D1_P   | IO_L15P_T2_DQS_34  | T20      | HDMIデータ1正                |

| HDMI_D1_N   | IO_L15N_T2_DQS_34  | U20      | HDMIデータ1負                |

| HDMI_D2_P   | IO_L14P_T2_SRCC_34 | N20      | HDMIデータ2正                |

| HDMI_D2_N   | IO_L14N_T2_SRCC_34 | P20      | HDMIデータ2負                |

| HDMI_SCL    | IO_L20N_T3_34      | R18      | HDMI IICクロック             |

| HDMI_SDA    | IO_L19P_T2_34      | R16      | HDMI IICデータ              |

| HDMI_CEC    | IO_L17P_T2_34      | Y18      | HDMIリモコン信号               |

| HDMI_HPD    | IO_L17N_T2_34      | Y19      | HDMIホットプラグ検出信号           |

| HDMI_OUT_EN | IO_L18P_T2_34      | V16      | HDMI電源出力制御               |

# 7.2 EEPROM 24LC04

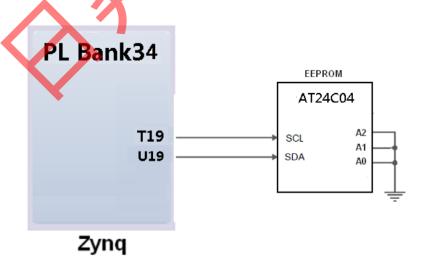

AX7020 開発ボードで、一枚の EEPROM を搭載。型番が 24LC04 で、容量は 4 Kbit(2\*256\*8bit)、二つの 256byte の block で構成されて、IIC バスで通信する。IIC バスの通信方式を学ぶために EEPROM を搭載している。EEPROM の I2C 信号は ZYNQ PL 側の BANK34 I0 ポートに接続する。図 7-5 は EPROM の回路図:

日昇テクノロジーなら可能にする

#### 図 7-5 EEPROM 回路図部分

図 7-6 EEPROM 実物図

### EEPROM ピンの割り当て:

| 信号名            | ZYNQ ピン名      | ZYNQ ピン番号 | 備考        |

|----------------|---------------|-----------|-----------|

| EEPROM_I2C_SCL | IO_25_34      | T19       | IICクロック信号 |

| EEPROM_I2C_SDA | IO_L12N_T1_34 | U19       | IICデータ信号  |

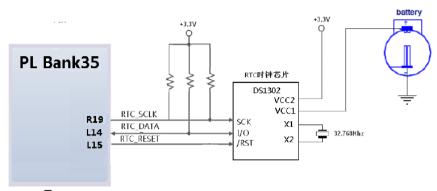

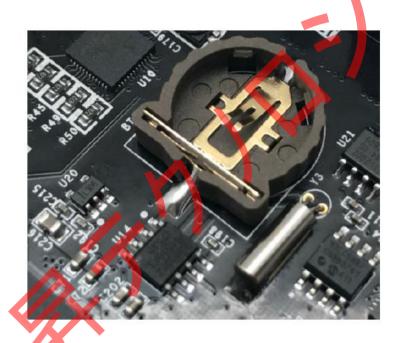

## 7.3 リアルタイムクロック DS1302

開発ボードに一枚の型番が DS1302 のリアルタイムクロック RTC チップを搭載。このチップは 2099 年までのカレンダー機能を提供する。システムでは時間機能が必要の場合、RTC は外部で一つの 32 768KHz のパッシブクロックを接続して、クロックチップに精確なクロックソースを提供し、RTC が精確なクロック情報を製品に提供できる。製品が電源切ってから、リアルタイムクロックは常に作業できるために、一つの電池をクロックチップに配置する。図 7~7 で BT1 は電池ホルダーで、コイン電池を入れると (型番 CR1220、電圧は 3V)、システムが電源切っても、コイン電池が DS1302 に給電できる。こうすることで、どんな場合で DS1302 が正常に作業できる。RTC のインターフェース信号も ZYNQ PL 側の BANK34 と BANK35 10 ポートと接続する。図 7~7 は DS1302 の回路図です:

Zynq

図 7-8 DS1302 実物図

# DS1302 インターフェースピンの割り当て:

| 信号名       | <b>ZYNQ</b> ピン名    | ZYNQ ピン番号 | 備考         |

|-----------|--------------------|-----------|------------|

| RTC _SCLK | IO_0_34            | R19       | RTCのクロック信号 |

| RTC_RESET | IO_L22N_T3_AD7N_35 | L15       | RTCのリセット信号 |

| RTC _DATA | IO_L22P_T3_AD7P_35 | L14       | RTCのデータ信号  |

保備格、高品質が不可能

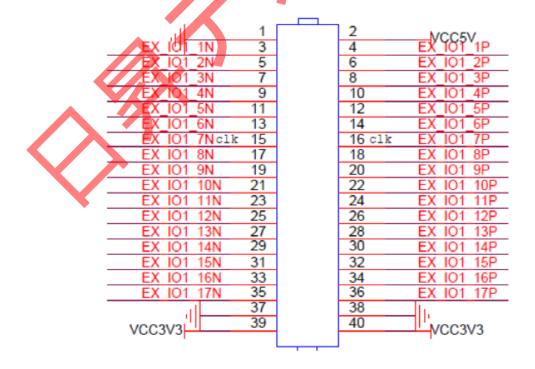

#### 7.4 拡張ポート J10

拡張ポート J10 は4 0 ピンの 2.54mmの 2 列コネクタで、もっと多いインターフェースとペリフェラルを拡張できる。オプションとして提供されているモジュールは ADDA モジュール、LCD モジュール、ギガビットイーサネットモジュール、音声入出力モジュール、マトリックスキーボードモジュール、500W 両眼視カメラモジュールなどを含む。拡張ポートには 5V 電源一つ、3.3V 電源 2 つ、GND 3 つ、10 ポート 34 つがある。10 ポートの信号は ZYNQ PL の BANK35 と BANK35 を接続する。レベルはデフォルトが 3.3V。拡張ポート J10 の一部分 I0 は開発ボードでの電源チップ (SPX3819M5-3-3) を変換して I0 のレベルを変更できる。 FPGA を焼損する恐れがあるので 5V のデバイスと直接に接続しないでください。もし 5V のデバイスと接続する場合、レベル転換チップを接続しなければならない。

拡張ポートと FPGA との間で 33 オムの抵抗を直列して FPGA を保護する。電圧あるいは電流が高すぎる場合は FPGA が損害しやすいので。PCB 設計での P と N の配線は差分配線を使用して、差分抵抗は 100 オムです。拡張ポートの回路図は図 7-9 の通りです:

# 図 7-9 J10 拡張ポートの回路図

図 7-10 は J10 拡張ポートの実物図です。拡張ポートの Pin1、Pin2 、 Pin39、Pin40 はボードで示す。

図 7-10 J10 拡張ポートの実物図

# 株式会社日昇テクノロジー

## J10 拡張ポートのピン割り当て:

| • | 1 1 2 T | H1 > - ( . |                |              |

|---|---------|------------|----------------|--------------|

|   | J10 ピン  | 信号名        | ZYNQ ピン名       | ZYNQ ピン番号    |

|   | PIN1    | GND        | -              | -            |

|   | PIN2    | +5V        | -              | -            |

|   | PIN3    | EX_IO1_1N  | IO_L22N_T3_34  | W19          |

|   | PIN4    | EX_IO1_1P  | IO_L22P_T3_34  | W18          |

|   | PIN5    | EX_IO1_2N  | IO_L6N_T0_34   | R14          |

|   | PIN6    | EX_IO1_2P  | IO_L6P_T0_34   | P14          |

|   | PIN7    | EX_IO1_3N  | IO_L7N_T1_34   | Y17          |

|   | PIN8    | EX_IO1_3P  | IO_L7P_T1_34   | Y16          |

|   | PIN9    | EX_IO1_4N  | IO_L10N_T1_34  | W15          |

|   | PIN10   | EX_IO1_4P  | IO_L10P_T1_34  | V15          |

|   | PIN11   | EX_IO1_5N  | IO_L8N_T1_34   | Y14          |

|   | PIN12   | EX_IO1_5P  | IO_L8P_T1_34   | W14          |

|   | PIN13   | EX_IO1_6N  | IO_L23N_T3_34  | P18          |

|   | PIN14   | EX_IO1_6P  | IO_L23P_T3_34  | N17          |

|   | PIN15   | EX_IO1_7N  | IO_L11N_T1_34  | U <b>1</b> 5 |

|   | PIN16   | EX_IO1_7P  | IO_L11P_T1_34  | U14          |

|   | PIN17   | EX_IO1_8N  | IO_L24N_T3_34  | P16          |

|   | PIN18   | EX_IO1_8P  | IO_L24P_T3_34  | P15          |

|   |         |            |                |              |

|   | PIN19   | EX_IO1_9N  | IO_L9N _T1_34  | U <b>1</b> 7 |

|   | PIN20   | EX_IO1_9P  | IO_L9P_T1_34   | T16          |

|   | PIN21   | EX_IO1_10N | IO_L21_N_T3_34 | V18          |

|   | PIN22   | EX_IO1_10P | IO_L21_P_T3_34 | V17          |

|   | PIN23   | EX_IO1_11N | IO_L5N_T0_34   | T15          |

|   | PIN24   | EX_IO1_11P | IO_L5P_T0_34   | T14          |

|   | PIN25   | EX_IO1_12N | IO_L3N_T0_34   | <b>V1</b> 3  |

|   | PIN26   | EX_IO1_12P | IO_L3P_T0_34   | U <b>1</b> 3 |

|   | PIN27   | EX_IO1_13N | IO_L4N_T0_34   | W13          |

|   | PIN28   | EX_IO1_13P | IO_L4P_T0_34   | V12          |

|   | PIN29   | EX_IO1_14N | IO_L2N_T0_34   | U12          |

| PIN30 | EX_IO1_14P | IO_L2P_T0_34 | T12 |

|-------|------------|--------------|-----|

| PIN31 | EX_IO1_15N | IO_L1N_T0_34 | T10 |

| PIN32 | EX_IO1_15P | IO_L1P_T0_34 | T11 |

| PIN33 | EX_IO1_16N | IO_L2N_T0_35 | A20 |

| PIN34 | EX_IO1_16P | IO_L2P_T0_35 | B19 |

| PIN35 | EX_IO1_17N | IO_L1N_T0_35 | B20 |

| PIN36 | EX_IO1_17P | IO_L1P_T0_35 | C20 |

| PIN37 | GND        | -            | -   |

| PIN38 | GND        | -            |     |

| PIN39 | +3.3V      | -            | -   |

| PIN40 | +3.3V      | -            | -   |

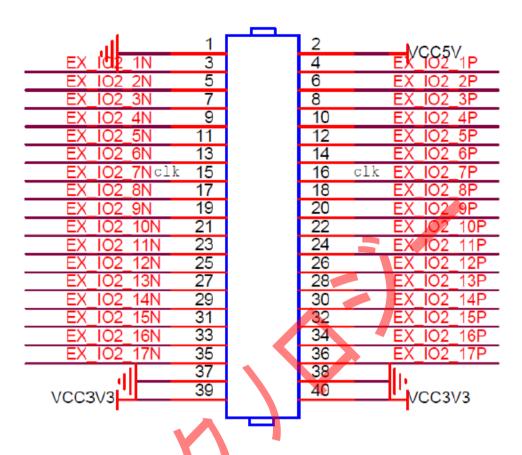

#### 7.5 拡張ポート J11

拡張ポート J11 は4 0 ピンの 2.54mmの 2 列コネクタで、もっと多いインターフェースとペリフェラルを拡張する。オプション品として提供されているモジュールは ADDA モジュール、LCD モジュール、ギガビットイーサネットモジュール、音声入出力モジュール、マトリックスキーボードモジュール、500W 両眼視カメラモジュールなどを含む。拡張ポートには 5V 電源 1 つ、3.3V 電源 2 つ、GND 3 つ、I0 ポート3 4 つがある。I0 ポートの信号は ZYNQ PL の BANK35 と接続する。レベルはデフォルトで 3.3V。拡張ポート J11 の全部 I0 は 開発ボードでの電源チップ (SPX3819M5-3-3) の変更で I0 のレベルを変更できる。FPGA を焼損する恐れがあるので 5V のデバイスと直接に接続しないでください。もし 5V のデバイスと接続する場合、レベル転換チップを接続しなければならない。

拡張ポートと FPGA との間で 33 オムの抵抗を直列して FPGA を保護する。そうしないと、電圧あるいは電流が高すぎる場合は FPGA が損害しやすい。PCB での P と N の配線は差分配線を使用して、差分抵抗は 100 オムです。拡張ポート (J11) の回路図は図 7-11 の通りです:

図 7-11 拡張ポートの回路図

図 7-12 は J11 拡張ポートの実物図です。拡張ポートの Pin1、Pin2 、Pin39、Pin40 はボードで示す。

図 7-12 J11 拡張ポートの実物図

# J11 の拡張ポートのピンの割り当て:

| <b>J11</b> ピン | 信号名                 | ZYNQ ピン名      | ZYNQ ピン番号    |

|---------------|---------------------|---------------|--------------|

| PIN1          | GND                 | -             | -            |

| PIN2          | +5V                 | -             | -            |

| P <b>I</b> N3 | EX_IO2_1N           | IO_L6N_T0_35  | F17          |

| PIN4          | EX_IO2_1P           | IO_L6P_T0_35  | F16          |

| PIN5          | EX_IO2_2N           | IO_L15N_T2_35 | F20          |

| PIN6          | EX_IO2_2P           | IO_L15P_T2_35 | F19          |

| PIN7          | EX_IO2_3N           | IO_L18N_T2_35 | G20          |

| PIN8          | EX_IO2_3P           | IO_L18P_T2_35 | G19          |

| PIN9          | EX_IO2_4N           | IO_L14N_T2_35 | H18          |

| PIN10         | EX_IO2_4P           | IO_L14P_T2_35 | J18          |

| PIN11         | EX_IO2_5N           | IO_L9N_T1_35  | L20          |

| PIN12         | EX_IO2_5P           | IO_L9P_T1_35  | L19          |

| PIN13         | EX_IO2_6N           | IO_L7N_T1_35  | M20          |

| PIN14         | EX_IO2_6P           | IO_L7P_T1_35  | M19          |

| PIN15         | EX_IO2_7N           | IO_L12N_T1_35 | K18          |

| PIN16         | EX_IO2_7P           | IO_L12P_T1_35 | K17          |

| PIN17         | EX_IO2_8N           | O_L10N_T1_35  | J <b>1</b> 9 |

|               |                     | -             |              |

| PIN18         | EX_IO2_8P           | IO_L10P_T1_35 | K19          |

| PIN19         | EX_102_9N           | IO_L17N_T2_35 | H20          |

| PIN20         | EX_102_9P           | IO_L17P_T2_35 | J20          |

| PIN21         | EX_IO2_10N          | IO_L11N_T1_35 | L17          |

| PIN22         | EX_IO2_10P          | IO_L11P_T1_35 | L16          |

| PIN23         | EX_ <b>I</b> O2_11N | IO_L8N_T1_35  | M18          |

| PIN24         | EX_ <b>I</b> O2_11P | IO_L8P_T1_35  | M17          |

| PIN25         | EX_IO2_12N          | IO_L4N_T0_35  | D20          |

| PIN26         | EX_IO2_12P          | IO_L4P_T0_35  | D <b>1</b> 9 |

| PIN27         | EX_IO2_13N          | IO_L5N_T0_35  | E <b>1</b> 9 |

| PIN28         | EX_IO2_13P          | IO_L5P_T0_35  | E18          |

| PIN29         | EX_IO2_14N          | IO_L16N_T2_35 | G18          |

| PIN30         | EX_IO2_14P          | IO_L16P_T2_35 | G <b>1</b> 7 |

| PIN31         | EX_IO2_15N          | IO_L13N_T2_35 | H17          |

| 日昇ナ | クノロ | シーカ | ム可能 | zŧ. |

|-----|-----|-----|-----|-----|

| PIN32 | EX_ <b>I</b> O2_15P | IO_L13P_T2_35 | H16 |

|-------|---------------------|---------------|-----|

| PIN33 | EX_IO2_16N          | IO_L19N_T3_35 | G15 |

| PIN34 | EX_ <b>I</b> O2_16P | IO_L19P_T3_35 | H15 |

| PIN35 | EX_ <b>I</b> O2_17N | IO_L20N_T3_35 | J14 |

| PIN36 | EX_ <b>I</b> O2_17P | IO_L20P_T3_35 | K14 |

| PIN37 | GND                 | -             | -   |

| PIN38 | GND                 | -             | -   |

| PIN39 | +3.3V               | -             | -   |

| PIN40 | +3.3V               | -             |     |

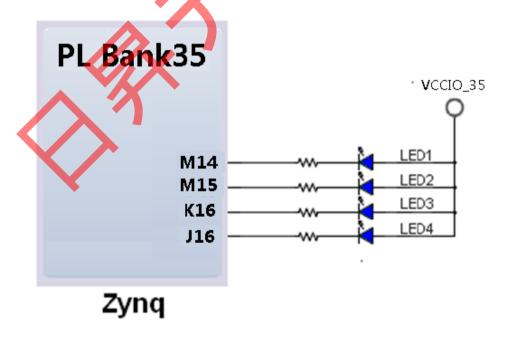

#### 7.6 ユーザーLED

AX7020 開発ボードの PL 部分は4つの LED 発光ダイオードと接続している。四つのユーザーLED 部分の回路図は図 7-13 のように表示する。LED ランプの信号は PL 部分 BANK35 の IO と接続する。PL 部分 BANK35 の IO ピンから出力するロジックは O のとき、LED が点灯され、1 のとき、LED が消灯される。

図 7-13 PL ユーザーLED の回路図

図 7-15 PL ユーザーLED の実物図

PL ユーザーLED のピンの割り当て:

| 信号名  | ZYNQ ピン名      | ZYNQ ピン番号 | 備考            |

|------|---------------|-----------|---------------|

| LED1 | IO_L23P_T3_35 | M14       | PLユーザーLED1ランプ |

| LED2 | IO_L23N_T3_35 | M15       | PLユーザーLED2ランプ |

| LED3 | IO_L24P_T3_35 | K16       | PLユーザーLED3ランプ |

| LED4 | IO_L24N_T3_35 | J16       | PLユーザーLED4ランプ |

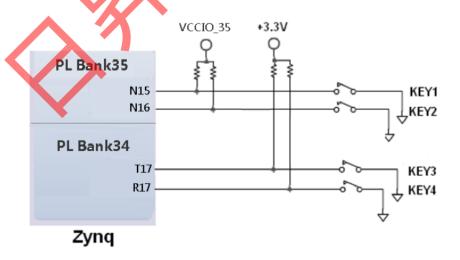

## 7.7 ユーザーキー

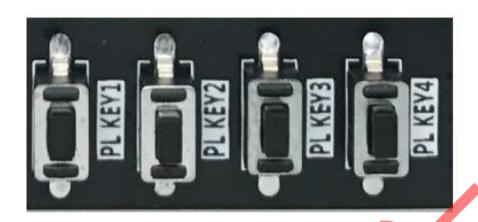

AX7020 開発ボードで、PL 部分に 4つのユーザーキー (KEY1~KEY4) が搭載されていて、キーの信号は ZYNQ の BANK34 と BANK35 の IO と接続する。キーは低レベル有効で、押下していない場合は信号が高く、押下する時、信号は低いレベルになる。四つのユーザーキーの回路図は図 7-16 の通り:

図 7-16 四つのユーザーキー回路図

図 7-17 四つの PL ユーザーキーの実物図

## キーのピン割り当て:

| · · · · · · · · · · · · · · · · · · · |               |          |           |

|---------------------------------------|---------------|----------|-----------|

| 信号名                                   | ZYNQ ピン名      | ZYNQピン番号 | 備考        |

| KEY1                                  | IO_L21P_T3_35 | N15      | PLユーザーキー1 |

| KEY2                                  | IO_L21P_T3_35 | N16      | PLユーザーキー2 |

| KEY3                                  | IO_L20P_T3_34 | T17      | PLユーザーキー3 |

| KEY4                                  | IO_L19N_T3_34 | R17      | PLユーザーキー4 |