# Xilinx Spartan6 XC6SLX9 ボードのマニュアル

copyright@2016

#### 修正履歴

| NO | バージョン  | 修正内容 | 修正日       |

|----|--------|------|-----------|

| 1  | Ver1.0 | 新規作成 | 2016/5/18 |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

- ※ この文書の情報は、文書を改善するため、事前の通知なく変更されることがあります。最新版は弊社ホームページからご参照ください。「http://www.csun.co.jp」

- ※ (株)日昇テクノロジーの書面による許可のない複製は、いかなる形態においても厳重に禁じられています。

## 目次

| 1 概要                 |    |

|----------------------|----|

| 2 電源                 | 6  |

| 3 FPGA               |    |

| 3.1 JTAG インタフェース     |    |

| 3.2 FPGA 電源及び GND ピン |    |

| 4 50M 水晶発振器          |    |

| 5 QSPI Flash         |    |

| 6 SDRAM              |    |

| 7 EEPROM 24LC04      |    |

| 8 リアルタイムクロック DS1302  | 15 |

| 9 USB からシリアルへの変換     |    |

| 10 VGA インターフェース      |    |

| 11 SD カードスロット        |    |

| 12 LED               |    |

| 13 ‡                 |    |

| 14 カメラインタフェース        | 22 |

| 158セグメントディスプレイ       |    |

| 16 ブザー               | 24 |

| 17 歴明 インタフェーフ        | 26 |

## 概要

本 FPGA 開発プラットフォームの機能について簡単に紹介する。

本開発ボードは Xilinx 会社の Spartan6 シリーズ FPGA を使用した。型番は XC6SLX9 で、256 ピンの BGA パッケ ージである。

#### 本開発ボードの FPGA リソースは下図のように:

|          |                               | Configurable Logic Blocks (CLBs) |            |                                | Block RAM Blocks                 |                      |          | Memory              |                                              |                                       | Takal                          |                       |                    |

|----------|-------------------------------|----------------------------------|------------|--------------------------------|----------------------------------|----------------------|----------|---------------------|----------------------------------------------|---------------------------------------|--------------------------------|-----------------------|--------------------|

| Device   | Logic<br>Cells <sup>(1)</sup> | Slices <sup>(2)</sup>            | Flip-Flops | Max<br>Distributed<br>RAM (Kb) | DSP48A1<br>Slices <sup>(3)</sup> | 18 Kb <sup>(4)</sup> | Max (Kb) | CMTs <sup>(5)</sup> | Controller<br>Blocks<br>(Max) <sup>(6)</sup> | Endpoint<br>Blocks for<br>PCI Express | Maximum<br>GTP<br>Transceivers | Total<br>I/O<br>Banks | Max<br>User<br>I/O |

| XC6SLX4  | 3,840                         | 600                              | 4,800      | 75                             | 8                                | 12                   | 216      | 2                   | 0                                            | 0                                     | 0                              | 4                     | 132                |

| XC6SLX9  | 9,152                         | 1,430                            | 11,440     | 90                             | 16                               | 32                   | 576      | 2                   | 2                                            | 0                                     | 0                              | 4                     | 200                |

| XC6SLX16 | 14,579                        | 2,278                            | 18,224     | 136                            | 32                               | 32                   | 576      | 2                   | 2                                            | 0                                     | 0                              | 4                     | 232                |

| XC6SLX25 | 24,051                        | 3,758                            | 30,064     | 229                            | 38                               | 52                   | 936      | 2                   | 2                                            | 0                                     | 0                              | 4                     | 266                |

| XC6SLX45 | 43,661                        | 6,822                            | 54,576     | 401                            | 58                               | 116                  | 2,088    | 4                   | 2                                            | 0                                     | 0                              | 4                     | 358                |

|          |                               |                                  |            |                                |                                  |                      |          |                     |                                              |                                       |                                |                       |                    |

#### 中に、主なパラメータは下記:

| パラメータ                    | 値                     |

|--------------------------|-----------------------|

| ロジックセル Logic Cells       | 9152                  |

| 乗数ラボ- DSP48              | 16                    |

| コンフィギャラブル ロジック ブロック CLBs | 90Kb                  |

| Block RAM                | 576Kb                 |

| クロック マネージメント タイル CMTs    | 2                     |

| IO数                      | 200                   |

| カーネル電圧                   | 1.15V-1.25V(お勧め 1.2V) |

| 動作温度                     | 0-85°C                |

|                          |                       |

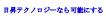

下図は全体のシステムの構造図である

#### 上記の構造図に通じて、この開発ボードによって実現できる機能は下記の通り:

- USB インターフェース給電。USB ケーブルで開発ボードに給電することができる。同時に、USB インターフェースは USB からシリアルへの変換の機能もあり、USB ケーブルを繋ぐと、パソコンとシリアル通信もできる。

- 256Mbit の SDRAM 搭載、データのキャッシュとして使用。

- 16Mbit の SPI FLASH を搭載、FPGAコンフィーグファイル及びユーザーデータを保存できる。

- VGA インターフェース x 1、16bit で、65536 色の表示サポート、カラー画像など表示できる。

- カメラインタフェース x 1、OV7670 カメラモジュール/OV5640 カメラモジュールと直結可能。

- RTC インタフェース x1(ノバッテリ型番は CR1220 である。

- 一つの IIC インターフェースの EEPROM 24LC04 を搭載。

- 50Mの水晶発振器 x 1、開発ボードに安定的なクロックを提供する。

- 4つの発光ダイオードLED。

- 4つのユーザーキー。

- 一つのブザーを搭載、SOS アラーム警報などの機能を実現できる。

- 6 つの 8SEG LED(アノードコモン LED)、動態的なスキャニングで数字の動態的な表示を実現。

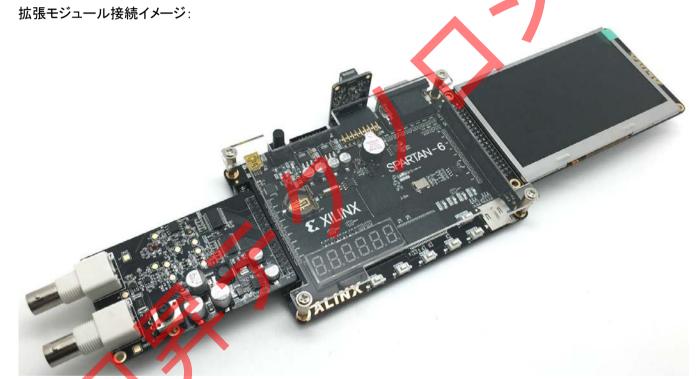

- 40 ピンの拡張インタフェース (2.54mm ピッチ) x 2、その中、34 個の IO ポート、5V 電源一つ、3.3V 電源二つと GND 三つを含まれる。二つの拡張モジュールを接続できる。例えば、4.3 インチの TFT 液晶と AD/DA などの拡張モジュールと繋ぐ。

- JTAG インタフェース、FPGA のデバッグ及びプログラミングに利用する。

- 一つの MicroSD カードソケット、SPI モードをサポートする。

## 2 電源

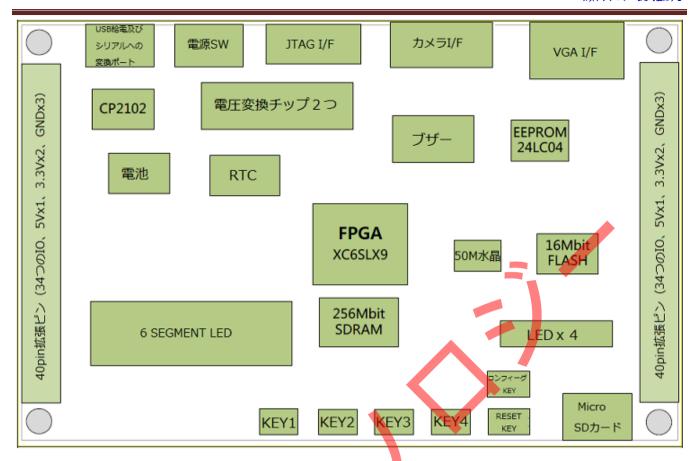

開発ボードの電源はUSBインタフェースによって提供される。2.1 図のように、JIはUSB 給電インターフェース、SWI はスイッチ、F1 は自動回復できるヒューズ。

図 2.1 電源

開発ボードは USB で給電し、2 つの LDO 電源チップで、1.2V 3.3V の電源を FPGA の BANK 電圧とカーネル電 圧を提供する。PCBを設計する時、4層のPCBを採用して、独立の電源層とGND層を保留している。これで、開発 ボードの電源が安定になれる。

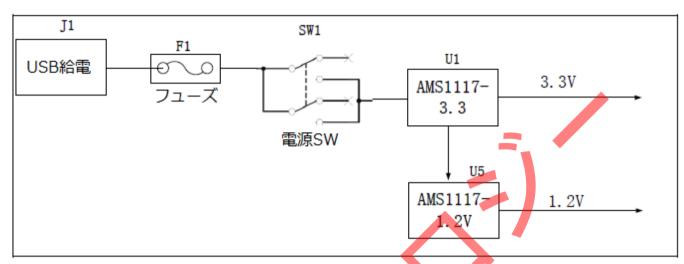

## 3 FPGA

本開発ボードで使用している XC6SLX9-2FTG256C 型番の FPGA は Xilinx 会社の Spartan6 シリーズの製品である。この型番は BGA でパッケージで、256 個のピンがある。ここで、FPGA ピンの意味をもう一度説明する。たくさんの製品に使用している FPGA は BGA パッケージではない、例えば、144 ピンと 208 ピンの FPGA チップ、これらのピン定義は1から 144、1から 208 などの数字で構成する。しかし、BGA パッケージのチップを使用している時、ピンの定義はアルファベット+数字の形になり、例えば E3、G3 など。だから、回路図を見る時、アルファベット+数字の形式でFPGA ピンを表示する。これを説明した上で、FPGA に関する各部分の機能を説明する。図 3.1 は開発ボードに使用している FPGA チップの実物図である。

2 0 1 11 G/( ) )

### 3.1 JTAG インタフェース

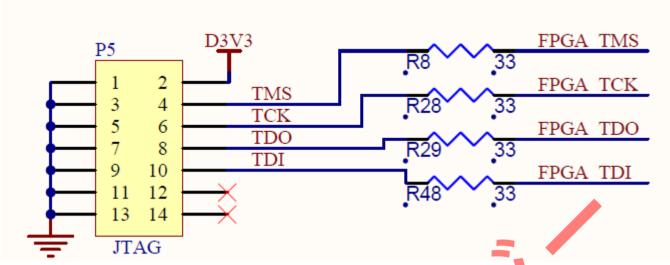

まず、FPGA のコンフィーグ及びデバッグインタフェース: JTAG インタフェースを説明する。

JTAG インダフェースの役割はコンパイルできたプログラム(. bit)を FPGA にダウンロードする或いは FLASH コンフィーグファイル(.mcs)を SPI FLASH にダウンロードする。bit ファイルを JTAG にダウンロードした後、電源切るとなくなるので、電源を接続して再ダウンロードしなければならない。mcs ファイルを FLASH にダウンロード後電源を切っても保存できる。

図 3 . 2 は JTAG インタフェース部分の回路図で、その中 TCK、TDO、TMS、TDI の 4 つの信号は FPGA ピンから引き出して33  $\Omega$  の抵抗を通じて JTAG コネクタと繋ぐ。

図3.2 JTAG インタフェイス部分の回路図

JTAG インタフェースは 14pin 2.0mm ピッチのコネクタを使用。

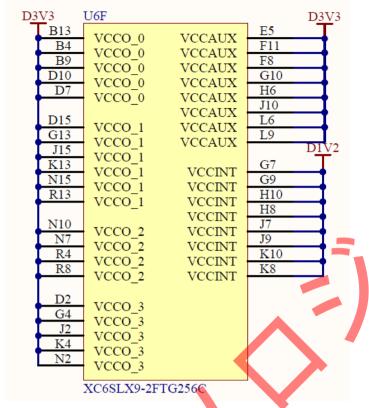

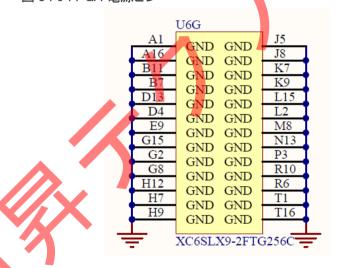

## 3.2 FPGA 電源及び GND ピン

次は、FPGA の電源ピン部分について説明する。中に bank ごとの電源ピンとコア電圧ピンを含む。図 3.6 のよう に、VCCINTは FPGA カーネル給電ピン、1.2Vと繋がる。VCCAUXは FPGA の補助給電ピン、3.3V 或いは 2.5V に 接続可能ですが、本ボードでは 3.3V に繋いている。VCCIO は FPGA の BANK の給電ピン。VCCIOO は FPGA の BANKO の給電ピン、VCCIO「・・・VCCIO3 は FPGA それぞれの BANK を対応して、すべて 3.3V の電圧と繋がる。つま り、対応の FPGA ピンは全て 3.3V で入力と出力する。具体的には、FPGA チップのデータシートをご参照ください。

図 3 . 6 FPGA 電源ピン

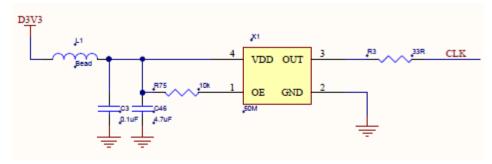

## 4 50M 水晶発振器

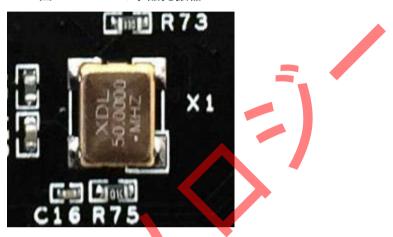

図 4.1 は上記説明した開発ボードにクロックを提供する 50M 水晶発振器で、FPGA の GCLK Pin T8 ピンを使用している。 GCLK で FPGA 内部のユーザーロジック回路をドライブする。 PLLs と DCMs を設定してもっと速いクロックを実現できる。 図 4.2 はの水晶発振器実物図。

図 4.1 50M の水晶発振器

図4.2 50M 水晶発振器の実物図。

#### クロックピンのアサイン:

| ピンネーム |  | FPGA ピン |

|-------|--|---------|

| CLK   |  | Т8      |

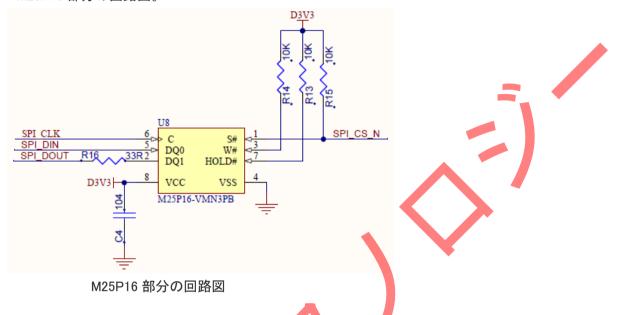

5 QSPI Flash

M25P16 は 16Mbit 容量のシリアル FLASH チップ。FPGA 中のプログラムをメモリするには、この容量は十分余裕です。FPGA の bit ファイル、アプリ及びユーザーデータもメモリできる。

| シルク | 型番     | 容量      | メーカー |

|-----|--------|---------|------|

| U8  | M25P16 | 16M bit | ST   |

#### M25P16 部分の回路図。

コンフィーグチップのピンアサイン:

| ピンネーム    | FPGA ピン |

|----------|---------|

| SPI_CLK  | R11     |

| SPI_CS_N | Т3      |

| SPI_DIN  | T10     |

| SPLDOUT  | P10     |

M25P16 の実物図

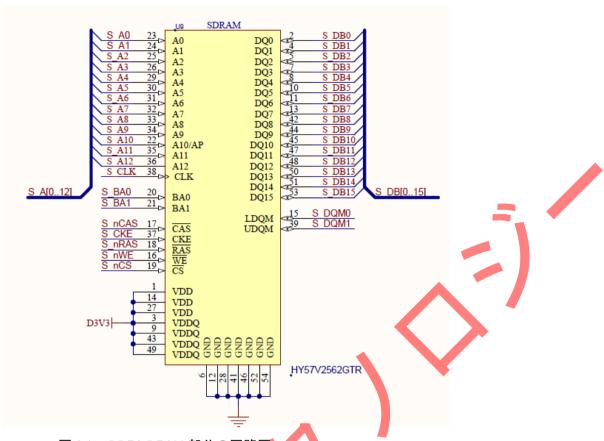

## 6 SDRAM

開発ボードに型番 HY57V2562GTR の SDRAM を搭載。容量は 256Mbit(16M\*16bit)、16bit バス。SDRAM は FPGA システムの中にパソコンのメモリのような役に相当して、FPGA システムのキャッシュエリアで、一時的にデータをメモリする。SDRAM はデータをキャッシュする。 例えばカメラから取集したデータを SDRAM にキャッシュして VGA インタ

#### フェースで表示する。

接続方式は下記図 6.1 のように。

図 6.1 DDR3 DRAM 部分の回路図

図 6.2 は SDRAM の実物図

図 5.2 SDRAM の実物図

#### SDRAM のピンアサイン:

| ピンネーム  | FPGA ピン |

|--------|---------|

| S_CLK  | H4      |

| S_CKE  | H2      |

| S_NCS  | G1      |

| S_NWE  | E1      |

| S_NCAS | F2      |

| S_NRAS | F1      |

## 株式会社日昇テクノロジー

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

| C DOM/0\  | Γ0 |

|-----------|----|

| S_DQM<0>  | E2 |

| S_DQM<1>  | H1 |

| S_BA<0>   | G6 |

| S_BA<1>   | J6 |

| S_A<0>    | J3 |

| S_A<1>    | J4 |

| S_A<2>    | К3 |

| S_A<3>    | K5 |

| S_A<4>    | P1 |

| S_A<5>    | N1 |

| S_A<6>    | M2 |

| S_A<7>    | M1 |

| S_A<8>    | L1 |

| S_A<9>    | K2 |

| S_A<10>   | K6 |

| S_A<11>   | K1 |

| S_A<12>   | JT |

| S_DB<0>   | A3 |

| S_DB<1>   | B3 |

| S_DB<2>   | A2 |

| S_DB<3>   | B2 |

| S_DB<4>   | B1 |

| S_DB<5>   | G2 |

| S_DB<6>   | C1 |

| S_DB<7>   | D1 |

| S_DB<8>   | H5 |

| S_DB<9>   | G5 |

| S_DB<10>  | H3 |

| S_DB<11>  | F6 |

| \$_DB<12> | G3 |

| S_DB<13>  | F5 |

| S_DB<14>  | F3 |

| S_DB<15>  | F4 |

|           |    |

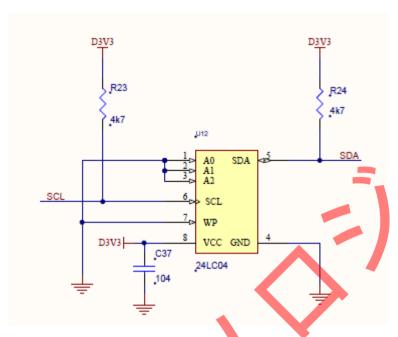

## **7 EEPROM 24LC04**

本開発ボードに一枚の型番 24LC04、容量 4Kbit(2 \* 256 \* 8bit)の EEPROM を搭載している。二つ 256byte の block で構成して、IIC バスによって通信する。図 7.1 は EEPROM の回路図。

図7.1 EEPROMの回路図部分

#### 図 7.2 EEPROM の実物図

図 7.2 EEPROM の実物図

#### EEPROM のピンアサイン

| ピンネーム | FPGA ピン |

|-------|---------|

| SDA   | P12     |

| SCL   | N12     |

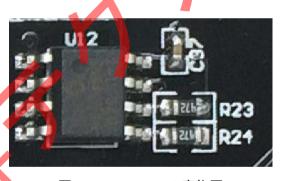

## 8 リアルタイムクロック DS1302

開発ボードに一つの型番 DS1302 のリアルタイムクロック RTC チップを搭載している。2099 年までのカレンダーを提供する。年月日時分秒と週がある。システム中に時間が必要な場合、RTC が製品にかかわる。クロックチップに正確なクロック源を提供するために、外部に32.768KHz のパッシブクロックを接続しなければならない。これでRTC が製品に正確なクロック源を提供できる。そして、製品の電源を切っても、リアルタイムクロックが正常に動作できるために、一つのバッテリを準備してクロックチップに給電する必要。図8.1 の中にU7 はバッテリ台座で、ボタン電池(型番 CR1220、電圧3 V)を入れると、システムがパワーダウンしても、ボタン電池が DS1302 に給電できる。このように、製品に電源があってもなくても、DS1302 が正常に動作できて、連続的な時間情報を提供する。図8.1 はDS1302 の回路図。

図 8.1 DS1302 の回路図

図 8.2 は DS1302 の実物図。

図 8.2 DS1302の実物図。

#### DS1302 インタフェースのピンアサイン:

| ピンネーム    | FPGA ピン |

|----------|---------|

| RTC_SCLK | E13     |

| RTC_nRST | C13     |

| RTC_DATA | D14     |

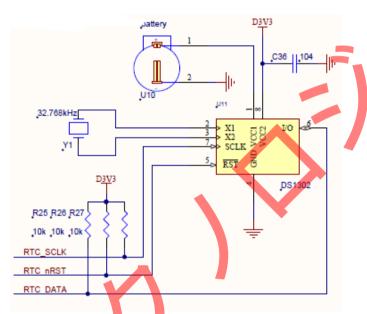

## 9 USB からシリアルへの変換

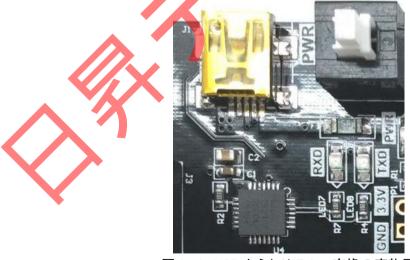

本ボードは Silicon Labs CP2102GM の USB-UART チップを搭載しております。USB インタフェースは Mini 型で、電源供給伴にシリアルへの変換機能がある。

回路図は図 9.1 のように

図 9.1 USB からシリアルへ変換の回路図

#### 図 9.2 は USB からシリアルへ変換の実物図

図 9.2 USB からシリアルへ変換の実物図

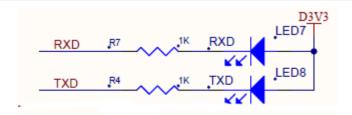

シリアル信号に2つの led(LED7,LED8)を搭載、シリアルポートにデータの送信と受信を示す。図9.3のように、

図 9.3 USB からシリアルへ変換の信号 LED

#### シリアルピンのアサイン:

| ピンネーム | FPGA ピン |  |  |

|-------|---------|--|--|

| RXD   | C11     |  |  |

| TXD   | D12     |  |  |

## 10 VGA インターフェース

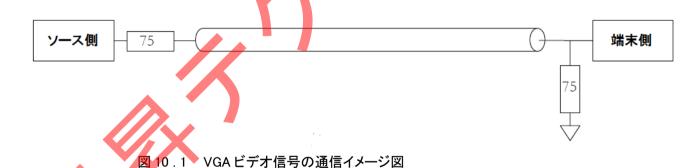

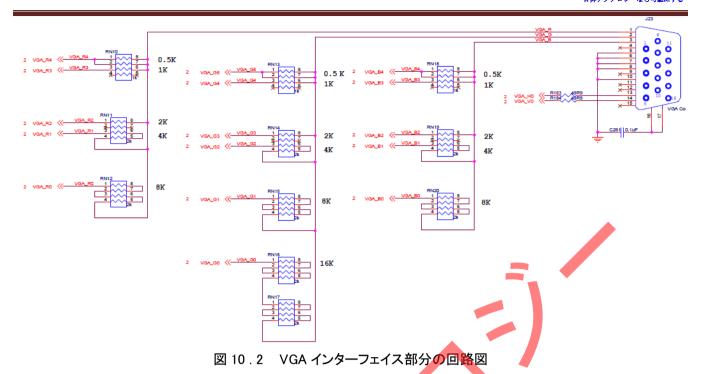

VGA インターフェースはディスプレイ設備に一番重要なインタフェースで、巨大な CRT ディスプレイ時代から、VGA インターフェースがよく使用されて、今まで利用されている。D-Sub インターフェースとも呼ばれる。

VGA インターフェースは D 型インタフェースで、合計 15 ピンがあり、3 行に分けて、1 行に 5 つピンがある。重要なのは 3 本の RGB カラー信号と 2 本のスキャン同期信号の HSYNC & VSYNC ピンである。

1、2、3 のピンはそれぞれ赤・緑・青の三原色模擬電圧で、0~0.714V peak-peak(ピーク-ピーク値)である。0V は無色、0.714V は満色を代表する。一部分の非標準ディスプレイは 1Vpp の満色電圧レベルを使用している。

三原色ソース側と端末側マッチング電気抵抗はすべて 75 オームである。図 10.1 のように。

HSYNCとVSYNCはそれぞれ水平同期信号と垂直同期信号、TTL電圧レベルである。FPGAはデジタル信号しか出力できない。VGAに必要なR、G、Bは全部アナログ信号だから、デジタルからアナログに変換必要である。 16bit 真カラー表示は2~16=65536種類の色が表示できる。RGBのビット数はそれぞれ5:6:5で、つまり、赤色は5位、

VGA インターフェースの回路図は図 10.2 のよう:

緑色は6位、青色は5位で表示する。

図 10.3 は VGA のインターフェース実物図

VGA インターフェースのピンアサイン

| ピン名前                   | FPGA ピン | 説明       |

|------------------------|---------|----------|

| VGA_D <b>&lt;0&gt;</b> | P7      | BLUE<0>  |

| VGA_D<1>               | M7      | BLUE<1>  |

| VGA_D<2>               | P8      | BLUE<2>  |

| VGA_D<3>               | N8      | BLUE<3>  |

| VGA_D<4>               | L7      | BLUE<4>  |

| VGA D<5>               | М9      | GREEN<0> |

| VGA_D<6>               | N9      | GREEN<1> |

| VGA_D<7>               | P9      | GREEN<2> |

| VGA_D<8>               | L10     | GREEN<3> |

| VGA_D<9>               | M10     | GREEN<4> |

| VGA_D<10>              | P11     | GREEN<5> |

| VGA_D<11>              | M11     | RED<0>   |

| VGA_D<12>              | M12     | RED<1>   |

| VGA_D<13>              | L12     | RED<2>   |

| VGA_D<14>              | N14     | RED<3>   |

18

| VGA_D<15> | M13 | RED<4>            |

|-----------|-----|-------------------|

| VGA_HS    | M14 | 行同期信 <del>号</del> |

| VGA_VS    | L13 | フレーム同期信号          |

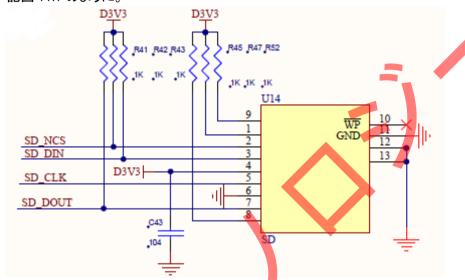

## 11 SD カードスロット

SDカード(Secure DigitalMemoryCard)は現在の消費デジタルデバイスの中に最も広く利用されてるメモリーデバイスである。本開発ボードで拡張した SD カードは SPI モードと SD モードをサポートする。SD カードは MicroSD カードである。回路図は下記図 11.1 のように。

図 11.1 SD カード部分の回路図

図 11.2 SD カードスロットの実物図

#### SD カードスロットピンアサイン

| SD モード  |         |  |

|---------|---------|--|

| ピン名前    | FPGA ピン |  |

| SD_NCS  | N3      |  |

| SD_DIN  | L5      |  |

| SD_CLK  | М3      |  |

| SD_DOUT | L4      |  |

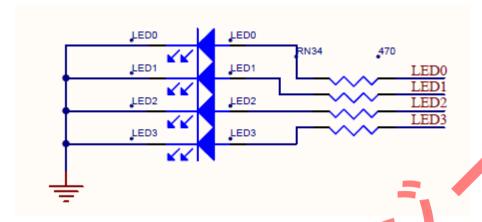

## **12 LED**

本開発ボードに4つの LED 発光ダイオードがあり、低レベル時点灯する、回路図は12.1 のように

図 12.1 LED の回路図

図 12.2 は LED 実物図

図 12.2 4つの LED 実物図

#### LED ピンアサイン

| ピン名前   | FPGA ピン |

|--------|---------|

| LED<0> | P4      |

| LEDX1> | N5      |

| LED<2> | P5      |

| LED<3> | M6      |

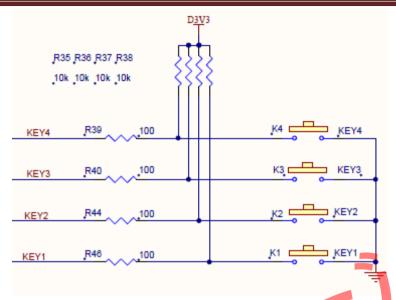

## 13 🛨

本開発ボードに6つの独立キーがあり、4つはユーザーキー(KEY1~KEY4)、2つは機能キー(PROGとRESET)。 低レベルの時有効になる。4つのユーザーキー回路図は13.1のように。

図 13.1 4つの独立キー回路図

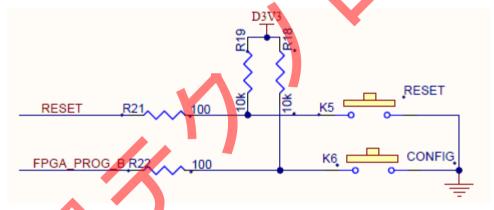

2つの機能キーの回路図は 13.2 のように。Reset キーは FPGA の GPIO に接続して、FPGA のプログラムのリセット に使用する。GONFIG キーは FPGA の専用ピン FPGA\_PROGRAM\_B に接続して、プログラムの再配置に使用 する。

図 13.2 2 つの機能キー回路図

#### 図 13.3 6 つの独立キー実物図

図 13.3 6 つの独立キー実物図

#### ボタンピンアサイン

| キー名前 | FPGA ピン | シール  |

|------|---------|------|

| KEY1 | C3      | KEY1 |

| KEY2 | D3      | KEY2 |

| KEY3 | E4      | KEY3 |

## 株式会社日昇テクノロジー

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

| KEY4  | E3 | KEY4 |

|-------|----|------|

| RESET | L3 | KEY5 |

| PROG  | T2 | KEY6 |

## 14 カメラインタフェース

本開発ボードは CMOS カメラモジュールのインタフェースを搭載している。 OV7670 のカメラモジュール と接続できて、ビデオ採集機能を実現する。採集した画像を TFT 液晶モニターや VGA インターフェースを通じてディスプレイで表示する。 OV7670 のカメラモジュール (カメラモジュールはオプションとして別売) 画素は 30W で、出力解像度は640\*480。

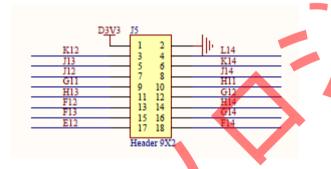

回路図は図 14.1 のように、

図 14.1 カメラインタフェースの回路図

#### カメラインターフェースのピンアサイン:

| FPGA ピン |

|---------|

| K12     |

| L14     |

| J13     |

| K14     |

| J12     |

| J14     |

| G11     |

| H11     |

| H13     |

| G12     |

| F12     |

| H14     |

| F13     |

| G14     |

| E12     |

| F14     |

|         |

## 158 セグメントディスプレイ

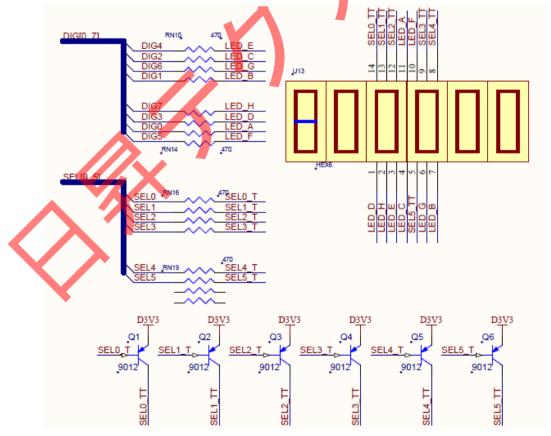

セグメントディスプレイはよく使われる表示装置で、普通は7セグメントディスプレイと8セグメントディスプレイがあり、 ふたつの違いはただ七7セグメントディスプレイより8セグメントディスプレイは一つの「. 」が多い。

本開発ボードで搭載しているのは6桁一体の8セグメントディスプレイで、その構造図は15.1のように:

図 15.1 セグメントディスプレイの構造

こちら使用しているのはアノードコモン LED で、あるセグメント対応のピンが低レベル時、相応するセグメントは明るくなって、それに対して、高レベルの時、点灯しない。

六位一体セグメントディスプレイはダイナミック表示に属する。人間の視覚時間差と発光ダイオードの残光効果により、各セグメントは同時に点灯しなくでも、スキャンの速度が十分速いなら、人間はそれがきらきらではなく一つの安定的な表示効果と見える。

六位一体セグメントディスプレイの同じセグメントが一つに繋ぎていて、合わせて8つのピンがあり、そして6つのコントロール信号ピンを加えて14つのピンになる。

図 15.2 のように、DIG[0..7]はセグメントの A、B、C、D、E、F、G、H(DP)を対応して、SEL [ 0..5]は 6 つセグメントの コントロールピンである。それも低レベルの時に有効になって、つまり、コントロールピンが低いレベルになっているとき、対応のセグメントが給電電圧があり、これでデジタル管が明るくなる。

図 15.2 セグメントディスプレイの回路図

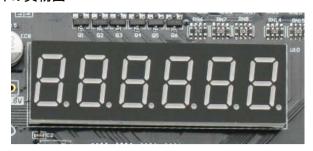

#### 図 15.3 セグメントディスプレイの実物図

図 15.3 セグメントディスプレイの実物図

#### セグメントディスプレイのピンアサイン

| ピン名前   | FPGA ピン | 説明       |  |

|--------|---------|----------|--|

| DIG[0] | C7      | セグメントA   |  |

| DIG[1] | E6      | セグメントB   |  |

| DIG[2] | C5      | セグメント C  |  |

| DIG[3] | F7      | セグメント D  |  |

| DIG[4] | D6      | セグメントE   |  |

| DIG[5] | E7      | セグメントF   |  |

| DIG[6] | D5      | セグメント G  |  |

| DIG[7] | C6      | セグメント DP |  |

| SEL[0] | D8      | 右側から1番   |  |

| SEL[1] | E8      | 右側から2番   |  |

| SEL[2] | F9      | 右側から3番   |  |

| SEL[3] | F10     | 右側から4番   |  |

| SEL[4] | E10     | 右側から5番   |  |

| SEL[5] | D9      | 右側から6番   |  |

## 16 ブザー

ブザーはトランジスタによってコントロールしている。低レベル時、トランジスタ通電して、ブザーが鳴り、高レベル時、トランジスタは締めて、ブザーが鳴らない。便利性を考えて、ブザーとFPGAの間にジャンパー(CB1、黄色い)を加えて、ブザーの音が嫌い時、ジャンパー(CB1)を取ればいい。

回路図は 16.1 のように

図 16.1 ブザーの回路図

#### ブザーピンのアサイン

| ピン名前   | FPGA ピン |  |

|--------|---------|--|

| BUZZER | J11     |  |

## 17 拡張インタフェース

開発ボードは2つの拡張インタフェースを予備している。40ピンがあり、この中、5Vの電源が1つ、3.3Vの電源が2つ、GNDが3つ、IOポートは34個である。これらのIOポートは全て独立IO口であり、ほかのインタフェースと共用していない。IOポートの電圧レベルはTTL3.3Vで、焼損しないように、使用している時、5Vのデバイスと直接繋ないではいけない。5Vのデバイスと接続する場合、レベル変換チップを繋がらなければならない。

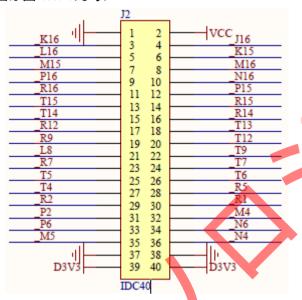

拡張インタフェース J2 の回路図は図 17.1 のように

図 17.1 J2 拡張インタフェースの回路図

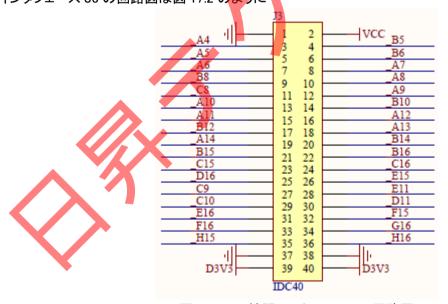

拡張インタフェース J3 の回路図は図 17.2 のように

図 17.2 J3 拡張インタフェースの回路図

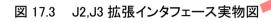

図 17.3 は J2,J3 拡張インタフェースの実物図である:

J2 拡張インタフェースピンアサイン

| ピン番号 | FPGA ピン | ピン番号 | FPGA ピン |

|------|---------|------|---------|

| 1    | GND     | 2    | VCC5V   |

| 3    | K16     | 4    | K15     |

| 5    | L16     | 6    | K15     |

| 7    | M15     | 8    | M16     |

| 9    | P16     | 10   | N16     |

| 11   | R16     | 12   | P15     |

| 13   | T15     | 14   | R15     |

| 15   | T14     | 16   | R14     |

## 株式会社日昇テクノロジー

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

| 17 | R12  | 18 | T13  |

|----|------|----|------|

| 19 | R9   | 20 | T12  |

| 21 | L8   | 22 | Т9   |

| 23 | R7   | 24 | T7   |

| 25 | Т5   | 26 | Т6   |

| 27 | T4   | 28 | R5   |

| 29 | R1   | 30 | R2   |

| 31 | P2   | 32 | M4   |

| 33 | P6   | 34 | N6   |

| 35 | M5   | 36 | N4   |

| 37 | GND  | 38 | GND  |

| 39 | D3V3 | 40 | D3V3 |

#### J3 拡張インタフェースピンアサイン

|      | , , , , , , , , , , , , , , , , , , , |      |            |

|------|---------------------------------------|------|------------|

| ピン番号 | FPGA ピン                               | ピン番号 | FPGA ピン    |

| 1    | GND                                   | 2    | VCC5V      |

| 3    | A4                                    | 4    | B5         |

| 5    | <b>A</b> 5                            | 6    | В6         |

| 7    | A6                                    | 8    | <b>A</b> 7 |

| 9    | B8                                    | 10   | A8         |

| 11   | C8                                    | 12   | A9         |

| 13   | A10                                   | 14   | B10        |

| 15   | A11                                   | 16   | A12        |

| 17   | B12                                   | 18   | A13        |

| 19   | A14                                   | 20   | B14        |

| 21   | B15                                   | 22   | B16        |

| 23   | C15                                   | 24   | C16        |

| 25   | D16                                   | 26   | E15        |

| 27   | <b>C</b> 9                            | 28   | E11        |

| 29   | C10                                   | 30   | D11        |

| 31   | E16                                   | 32   | F15        |

| 33   | F16                                   | 34   | G16        |

| 35   | H16                                   | 36   | H16        |

| 37   | GND                                   | 38   | GND        |

| 39   | D3V3                                  | 40   | D3V3       |

以上。