# Xilinx Spartan6 XC6SLX45 ボードのマニュアル

# 株式会社日昇テクノロジー

copyright@2017~

# 修正履歴

| NO | バージョン  | 修正内容                    | 修正日       |

|----|--------|-------------------------|-----------|

| 1  | Ver1.0 | 新規作成                    | 2017/1/20 |

| 2  | Ver1.1 | ハードウェア変更                | 2017/4/11 |

|    |        | DVI 出カインタフェースを削除と共に VGA |           |

|    |        | 出カチップを変更                |           |

|    |        |                         |           |

|    |        |                         |           |

|    |        |                         |           |

|    |        |                         |           |

|    |        |                         |           |

|    |        |                         |           |

|    |        |                         |           |

- ※ この文書の情報は、文書を改善するため、事前の通知なく変更されることがあります。最新版は弊社ホームページからご参照ください。「http://www.csun.co.jp」

- ※ (株)日昇テクノロジーの書面による許可のない複製は、いかなる形態においても厳重に禁じられています。

# 目次

| 1  | 概要                  | . 4  |

|----|---------------------|------|

| 2  | コアボード               | . 6  |

|    | 2.1 概要              | . 7  |

|    | 2.2 DDR3            | . 7  |

|    | 2.3 SPI Flash       | 10   |

|    | 2.4 FPGA 給電電源       | . 11 |

|    | 2.5 拡張インタフェース       | . 13 |

|    | 2.6 電源インタフェース       | . 15 |

|    | 2.7 外部発振器           | 16   |

|    | 2.8 LED             | 17   |

|    | 2.9 コアボード PCB サイズ   | . 18 |

| 3. | 拡張ボード               | 20   |

|    | 3.1 概要              | 20   |

|    | 3.2 VGA インタフェース     | 21   |

|    | 3.3 HDMI 出力インタフェース  | 23   |

|    | 3.4 HDMI 入力インタフェース  | 26   |

|    | 3.5 ビデオ入力インタフェース    | . 28 |

|    | 3.6 ギガイーサネットインタフェース | 29   |

|    | 3.7 ARM コントローラ      | 31   |

|    | 3.7.1 リアルタイムクロック    |      |

|    | 3.7.2 EEPROM        | 33   |

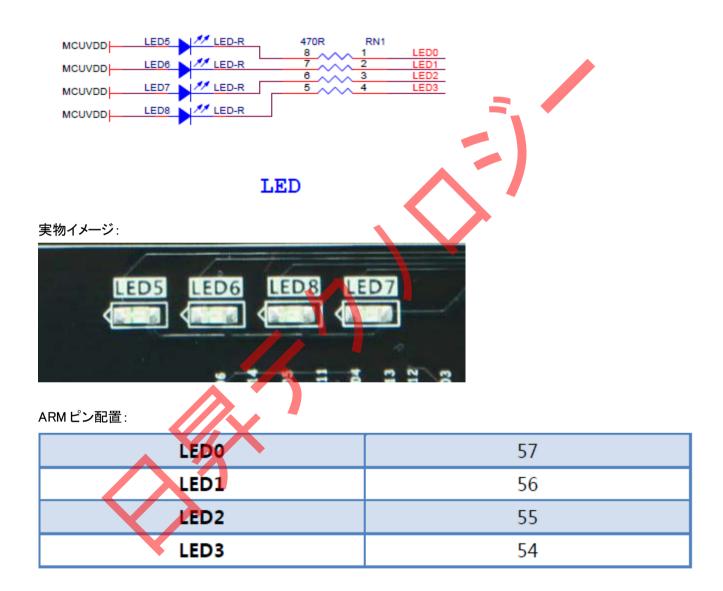

|    | 3.7.3 LED           |      |

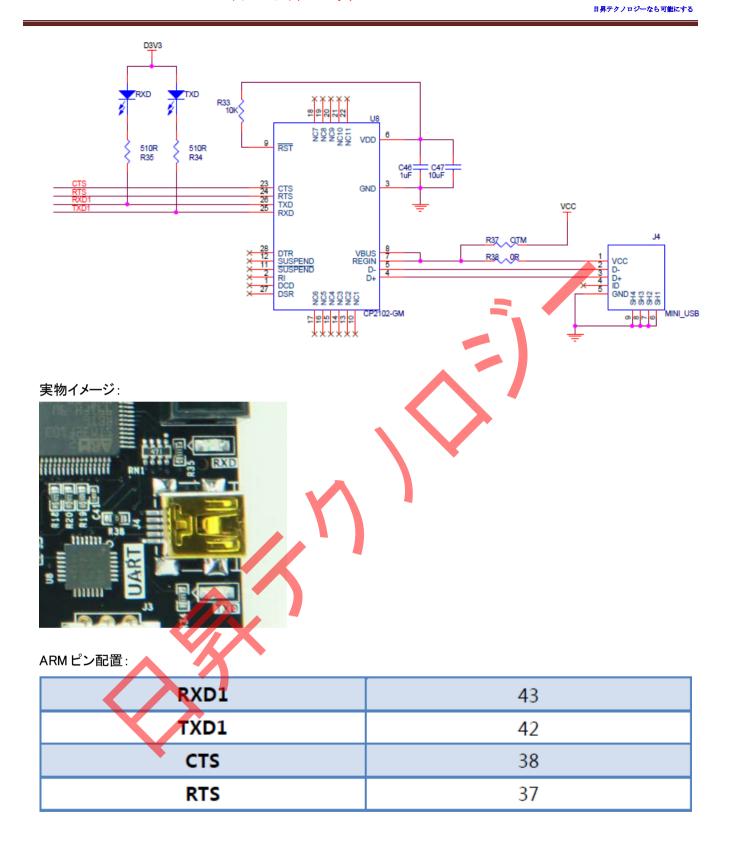

|    | 3.7.4 USB シリアルポート   |      |

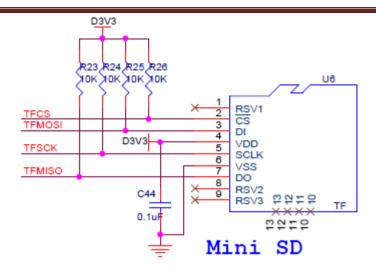

|    | 3.7.5 SD カード        | 35   |

|    | 3.8 CMOS カメラ I/F    | 36   |

|    | 3.9 拡張インタフェース       |      |

|    | 3.10 JTAG インタフェース   | 40   |

|    | 3.11 +              | 41   |

|    |                     | 4.4  |

# 1 概要

本 FPGA 開発プラットフォームの機能について簡単に紹介する。

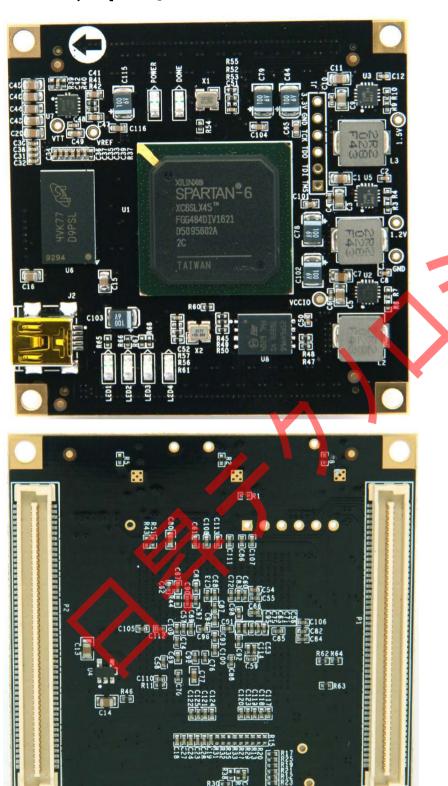

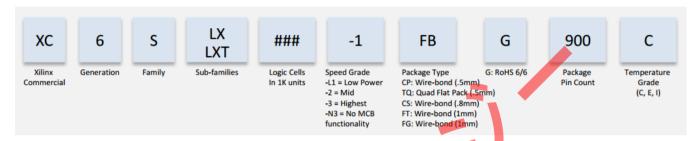

本開発ボードは Xilinx 会社の Spartan6 シリーズ FPGA を使用した。型番は XC6SLX45-2FG484 で、BGA 484 パッケージである。

本開発ボードはコアボードと拡張ボードで構成。コアボードは主に FPGA+DDR3+FLASH で構成。Spartan6 FPGA 内部でハードウェアの DDR コントローラが集合されて DDR3 との間の通信のクロックは 333MHz にもあり、DDR3 内部は 666MHz で、4チャネルの 1080p ビデオ処理にも十分な処理能力を満足している。

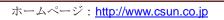

#### 下図は全体のシステムの構造図である:

上記の構造図に通じて、この開発ボードによって実現できる機能は下記の通り:

- USB インターフェース給電。USB ケーブルで開発ボードに給電することができる。同時に、USB インターフェースは USB からシリアルへの変換の機能もあり、USB ケーブルを繋ぐと、パソコンとシリアル通信もできる。

- 2Gbit の DDR3 を搭載、データのキャッシュとして使用。

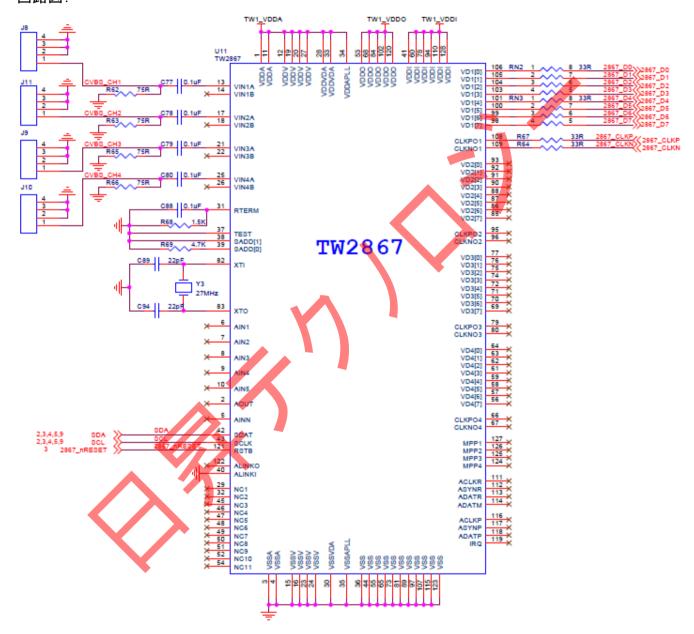

- AV IN インターフェース x 4、Techwell 社の TW2867 を採用、PAL/NTSC/SECAM 自動認識し、BT656 出力、多チャネルでバス共用できる。

- VGA 出力インターフェース x 1、ADI 社の ADV7123 を採用、240Mhz のクロック出力と 1080P@60Hz の 解像度をサポートする。

コロニ とうしょう みと 可能による

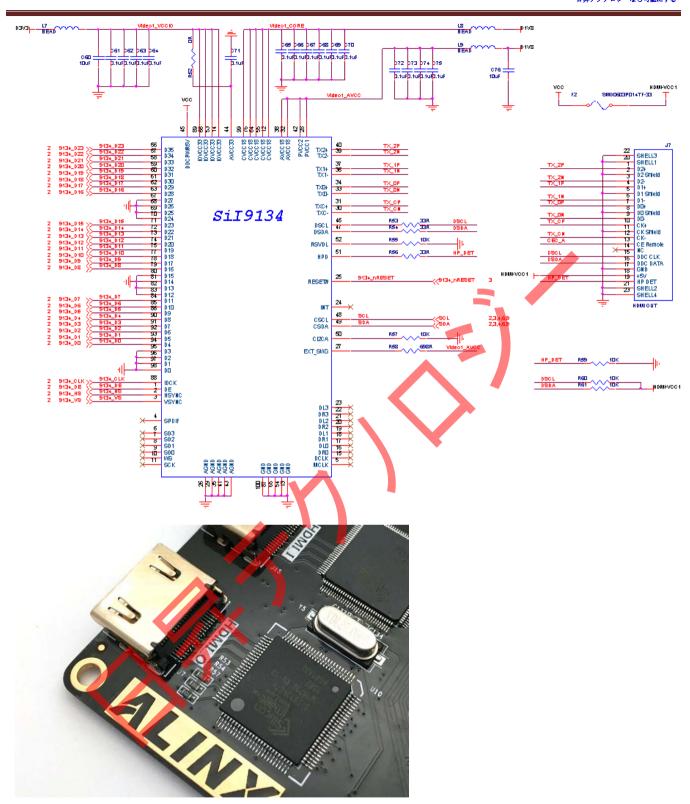

- HDMI 出力インターフェース x 1、Silion Image 社の SIL9134 を採用、1080P@60Hz の出力、3D 出力をサポートする。

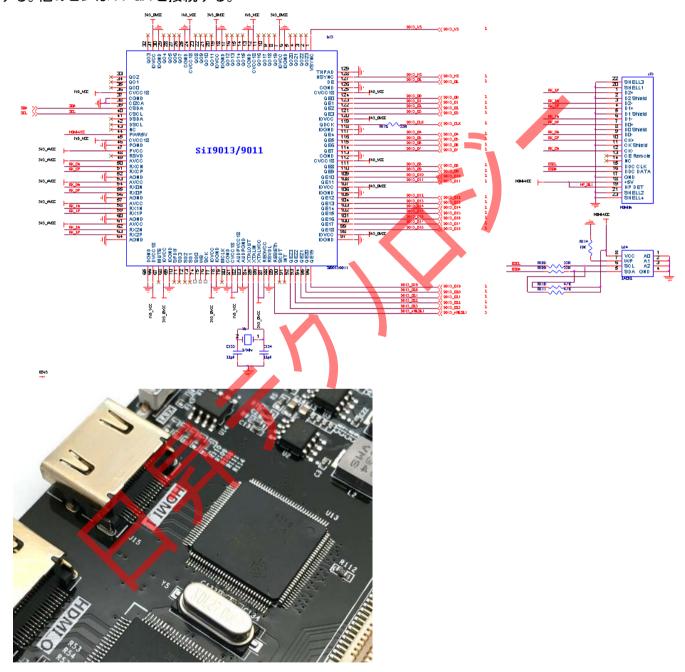

- HDMI 入力インターフェース x 1、Silion Image 社の SIL9013 を採用、1080P@60Hz の入力、多種のフォーマットのデータをサポートする。

- カメラインタフェース x 1、OV7670 カメラモジュール/OV5640 カメラモジュールと直結可能。

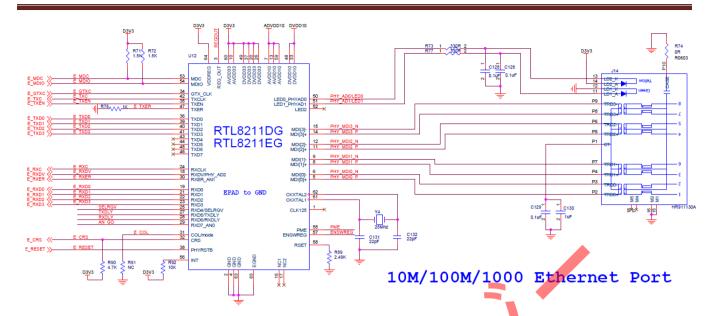

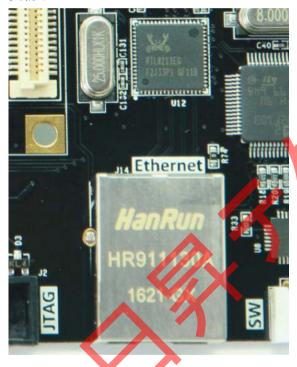

- 10/100M/1000M イーサネット RJ-45 インタフェース x 1、Realtek 社の RTL8211EG を採用。

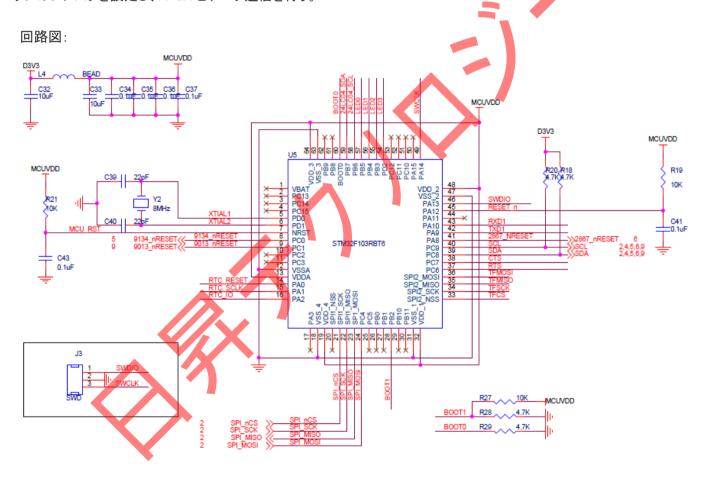

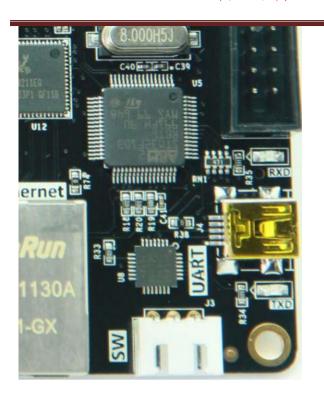

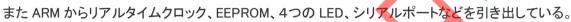

また、拡張ボードには ARM チップ (STM32F103)を搭載して I2C で各インタフェースチップと FPGA を設定する。

# 2 コアボード

## 2.1 概要

コアボードは主に FPGA+DDR3+FLASH で構成。

メインチップの FPGA は Xilinx 会社の Spartan6 シリーズ FPGA を使用。型番は XC6SLX45-2FG484I で、BGA 484パッケージである。DDR3 は MICRON 社の MT41J128M16LA-187E を採用。容量は 2Gbit、16bit バス。

また 168 個の IO を引出ている。

PCB サイズは 60\*60(mm)。

#### (1) FPGA

#### XC6SLX45-2FG484Iの主なパラメータ:

| 項目                       | 値                  |

|--------------------------|--------------------|

| Logic Cells              | 43,661             |

| Slices                   | 6,822              |

| CLB flip-flops           | 54,576             |

| Block RAM(kb) size       | 2,088              |

| CMT                      | 4                  |

| DSP48A1 Slices           | 58                 |

| Memory Controller Blocks | 2                  |

| Package                  | BGA484,1.0mm pitch |

| Speed                    | -2                 |

| Temprature               | Industrial class   |

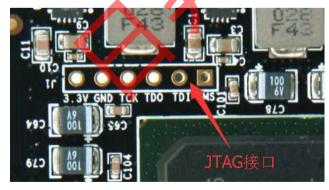

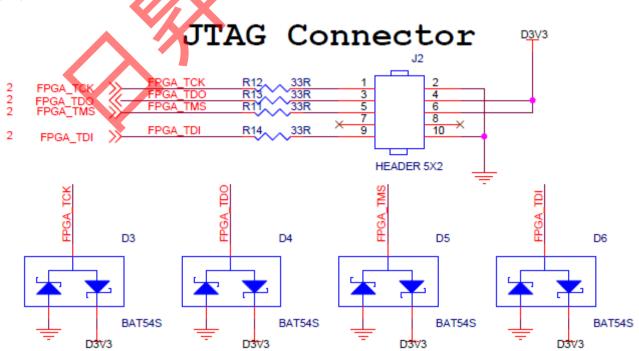

#### (2) JTAG インタフェース

コアボードに JTAG インタフェースを予備しております。拡張ボードなくてもダウンロード及びデバッグが可能です。

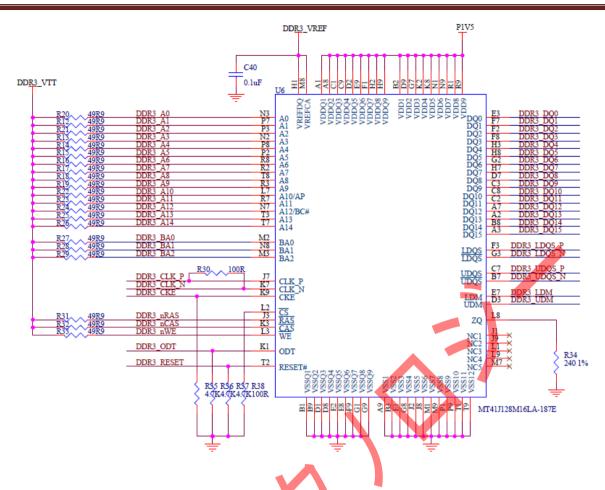

#### 2.2 DDR3

#### DDR3 部分の回路図:

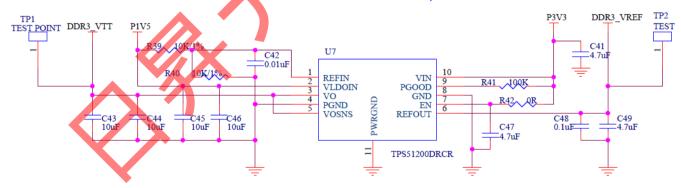

また DDR3 のアドレスバスとコントロールバスの為に VTT 電源と DDR3 の基準電圧 VREF を提供する必要。二つとも 1.5V。 回路図は下記:

#### DDR3 POWER For VTT/VREF

DDR3 実物及び電圧部分のイメージ:

FPGA の BANK3 と接続する。詳しくは UCF ファイルをご参照ください。

| Pin Name   | FPGA Pin   | Pin Name   | FPGA Pin |

|------------|------------|------------|----------|

| DDR3_A[0]  | H2         | DDR3_A[11] | C1       |

| DDR3_A[1]  | H1         | DDR3_A[12] | D1       |

| DDR3_A[2]  | H5         | DDR3_A[13] | G6       |

| DDR3_A[3]  | K6         | DDR3_A[14] | F5       |

| DDR3_A[4]  | F3         | DDR3_BA[0] | G3       |

| DDR3_A[5]  | <b>K</b> 3 | DDR3_BA[1] | G1       |

| DDR3_A[6]  | J4         | DDR3_BA[2] | F1       |

| DDR3_A[7]  | H6         | DDR3_nCAS  | K4       |

| DDR3_A[8]  | E3         | DDR3_CKE   | D2       |

| DDR3_A[9]  | E1         | DDR3_CLK_P | H4       |

| DDR3_A[10] | G4         | DDR3_CLK_N | H3       |

L1

T2

T1

DDR3 nRAS DDR3 DQ[8] K5 P2 DDR3 nWE F2 DDR3 DQ[9] P1 DDR3\_DQ[10] DDR3 ODT J6 R3 DDR3\_DQ[11] DDR3 RESET C3 R1 DDR3\_DQ[12] DDR3 LDM 14 U3 **DDR3 UDM** DDR3 DQ[13] M3 U1 DDR3\_DQ[14] DDR3 DQ[0] V2 N3 DDR3\_DQ[1] DDR3\_DQ[15] N1 V1 DDR3\_LDQS\_P DDR3\_DQ[2] M2 L3

DDR3\_LDQS\_N

DDR3\_UDQS\_P

DDR3\_UDQS\_N

## 2.3 SPI Flash

DDR3\_DQ[3]

DDR3\_DQ[4]

DDR3\_DQ[5]

DDR3\_DQ[6]

DDR3\_DQ[7]

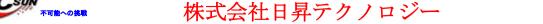

ST 社の型番 M25P64 の SPI Flash を搭載。容量は 64Mbit、3.3V CMOS 電圧。

M1

J3

J1

K2

K1

#### Pin 配置:

| 引脚名称     | FPGA 引脚 |

|----------|---------|

| SPI_CLK  | Y21     |

| SPI_CSn  | T5      |

| SPI_DIN  | AB20    |

| SPI_DOUT | AA20    |

回路図:

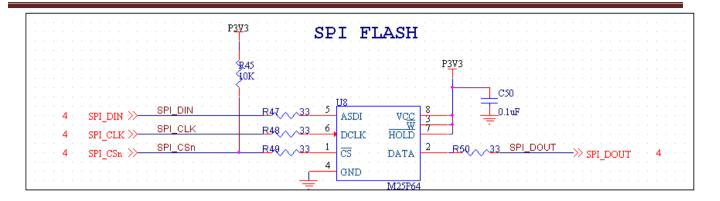

#### 実物イメージ:

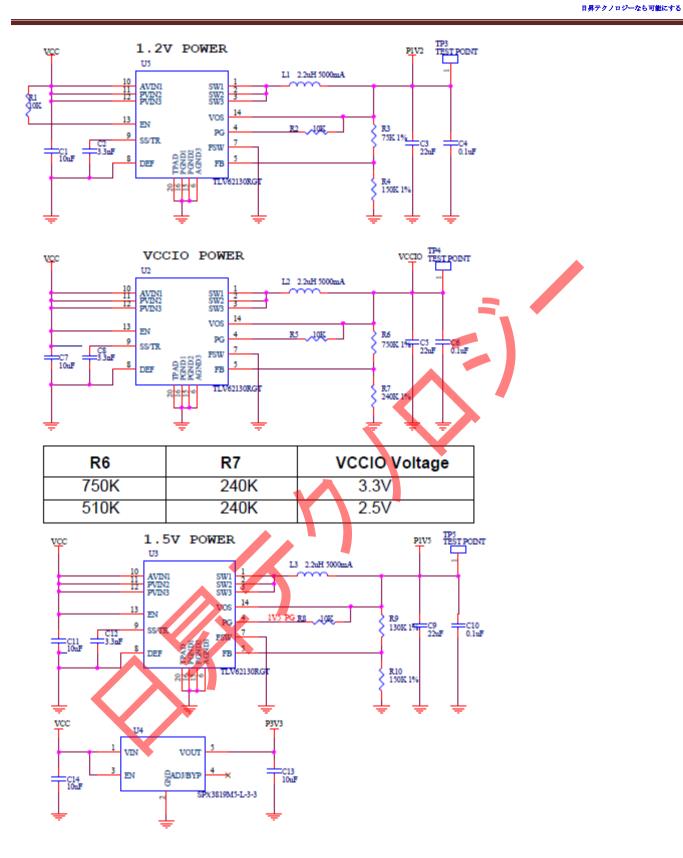

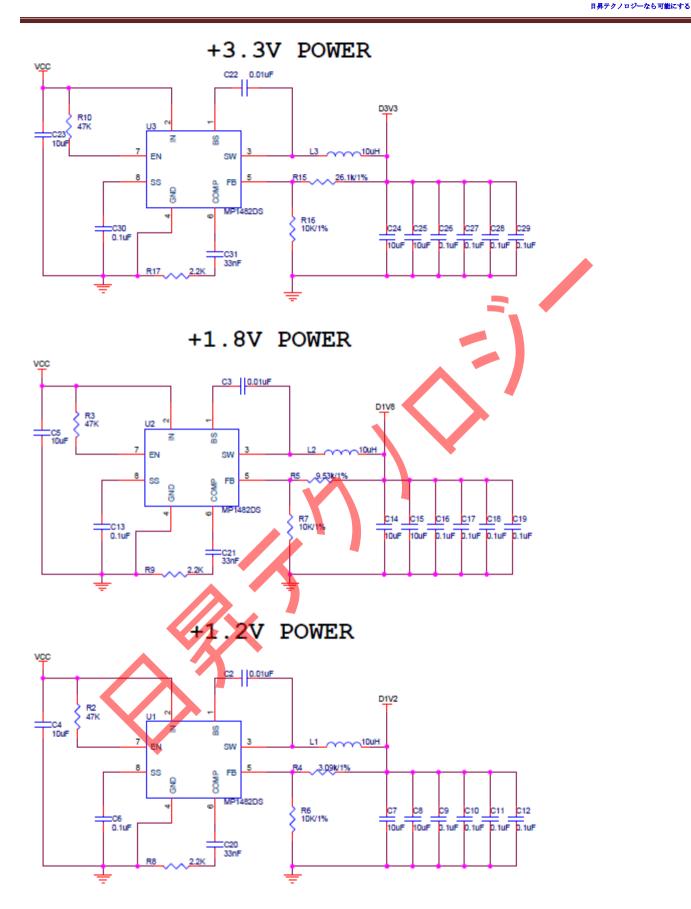

## 2.4 FPGA 給電電源

FPGA が正常に動作するには、P3V3、P1V2 と VCCIO 三つの電源を提供する必要。P3V3 は FPGA の VCCAUX に電源を提供する、電圧は3.3V。P1V2 は FPGA の VCCINT に電源を提供する、電圧は1.2V。 VCCIO は FPGA の BANKO, BANKI, BANK2 の VCCO に電源を提供する。また DDR3 も P1V5 が必要、 電圧は 1.5V(VTT と VREF を生成する)。

三つの電源は(P1V2, VCCIO, P1V5)TI 社の TLV62130RGT DCDC チップで実現。P3V3 は電流が小さい ので LDO チップ SPX3819M5-L-3-3 で実現。

#### 回路図:

実物イメージ:

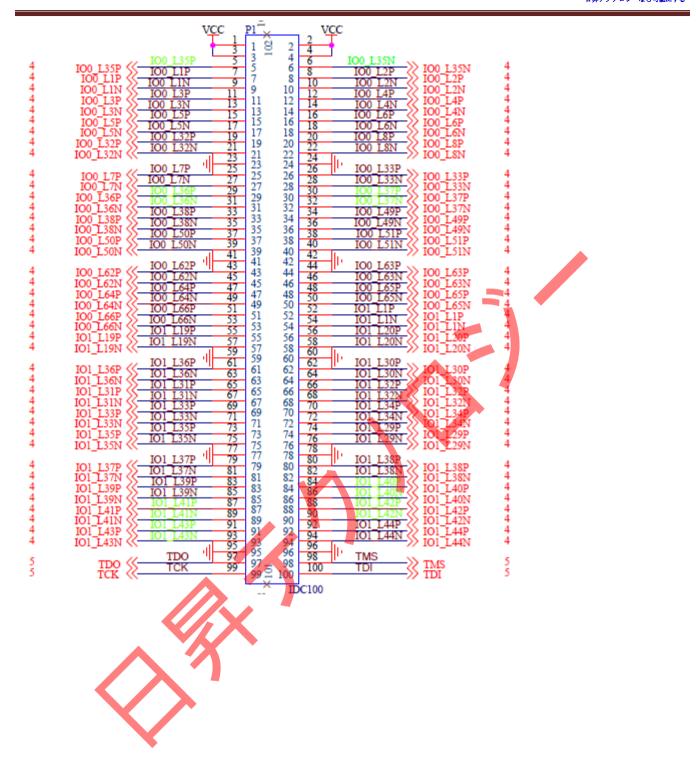

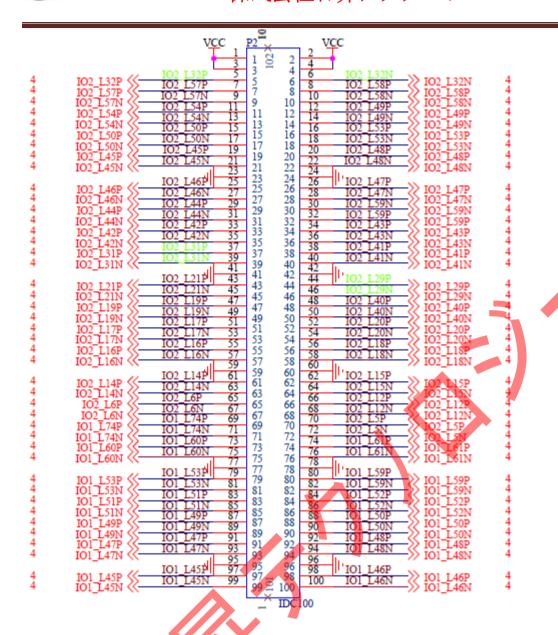

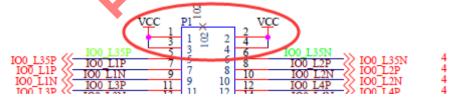

# 2.5 拡張インタフェース

コアボードから2つの拡張インタフェースを引出、100pin x 2 のコネクタで拡張ボードと繋ぐ。 コネクタは AMP TYCO BTB、型番 5177984-4 を使用。0.8mm ピッチ、高さは 5mm。 拡張ボード上は型番 5177983-4 のコネクタを使用。

# 2.6 電源インタフェース

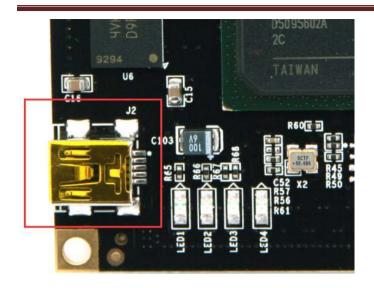

コアボードを正常に動作させる為に、拡張ボードからインタフェースを通して 5V の電源を提供する必要。コアボードの動作電圧範囲は 4.5V~5.5V、電流は 1A 前後なので、拡張ボード側の電源は 5V/2A がお勧め。 5V 電源は拡張インタフェースの P1,P2 の 1~4Pin(VCC)でコアボードに提供される。

もしコアボードだけ動作する場合は、Mini USB インタフェース(J2)で電源供給かのうです。 注意点:拡張ボード給電と J2 給電同時には使用しないでください。どちらか一つだけにしてください。

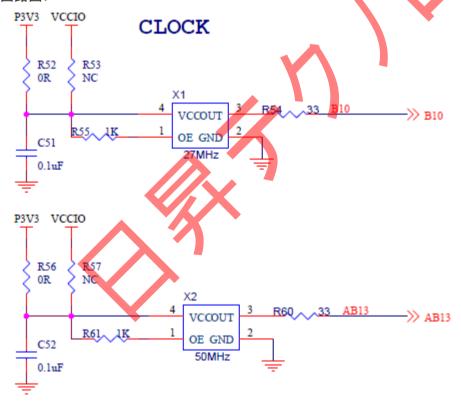

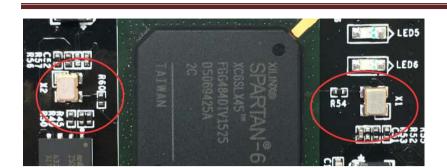

# 2.7 外部発振器

コアボードに 50M 水晶発振器と 27M 水晶発振器を搭載。50MHz クロックは FPGA の AB13 ピンと接続し、27MHz クロックは FPGA の B10 ピンと接続する。

#### 回路図:

実物イメージ:

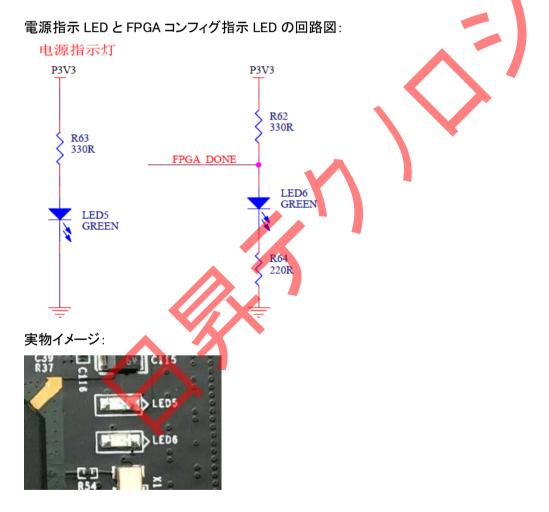

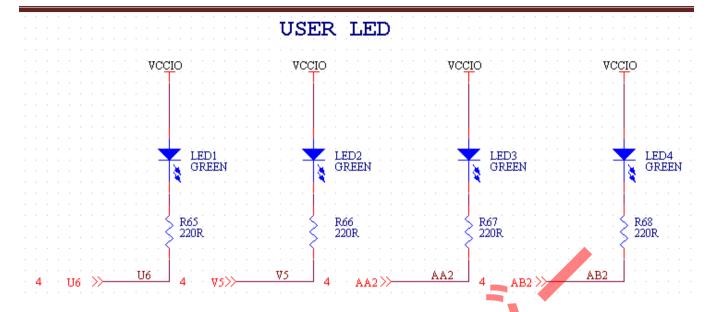

## 2.8 LED

コアボードに6つの LED 発光ダイオードがあり、4つはユーザーLED、1つは電源指示 LED、1つは FPGA コンフィグ指示 LED。電源指示 LED はP3V3と繋、3.3V 電圧が正常な場合、LED は点灯する。FPGA コンフィグ指示 LED は FPGA コンフィグ成功時点灯、失敗したら消灯する。

4つのユーザーLED について、低レベル時点灯する。 回路図:

#### LED 実物イメージ:

#### FPGA ピン配置:

| LED 名称 | FPGA 引脚 |

|--------|---------|

| LED0   | U6      |

| LED1   | V5      |

| LED2   | AA2     |

| LED3   | AB2     |

# 2.9 コアボード PCB サイズ

表面:

# 3. 拡張ボード

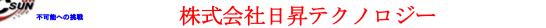

# 3.1 概要

#### 主な機能:

- ・4チャネルのビデオ入力(TW2867)

- 1チャネルのHDMI入力(SiI9013)

- 1チャネルのVGA出力(ADV7123)

- 1チャネルのHDMI出力(SiI9134)

- •1チャネルのギガイーサネットI/F(RTL8211E)

- ・1チャネルのCMOS入力

- •1つのARMチップ(STM32F103)

#### 主なサンプル:

01\_led\_test LEDテスト

02\_ddr3\_test DDR3テスト

03\_i2c\_slave I2C通信テスト

04\_color\_bar color bar VGA出力テスト

05\_color\_bar\_ycbcr YCbCr色空間color bar HDMI出力テスト

06\_ycbcr\_to\_rgb YCbCr色空間からRGB色空間に変換テスト

07\_rgb\_to\_ycbcr RGB色空間からYCbCr色空間に変換テスト

08 ycbcr444 to ycbcr422 YCbCr444からYCbCr422色空間に変換テスト

09\_hdmi\_input\_loopback HDMI入力ループテスト(バッファ無し)

10\_hdmi\_input\_loopback\_ddr HDMI入力ループテスト(DDRバッファあり)

11\_ov5640\_display OV5640カメラ表示テスト(VGA/HDMIで画像表示)

12\_cvbs\_display CVBS表示テスト

13 double cvbs pip 2チャネルのCVBS表示(PIP)テスト

14\_red\_blue\_3d 赤と青の3Dテスト

15\_quad\_cvbs\_display 4チャネルのCVBS表示テスト

16\_freeze ビデオフレーム凍結テスト

17\_sobel sobelエッジ検出テスト

18 osd OSDテスト

19\_ethernet\_test Ethernetテスト

20\_ov5640\_ethernet\_800600 カメラとEthernetテスト(画像をイーサネットでPCに転送し表示する)

21\_7lcd\_test 7インチLCD表示テスト

22\_full\_test 総合テスト(Ethernet、HDMI入力、VGA出力、HDMI出力、CMOS入力、DDR動作状態、LEDなど)

23 ov5640 7lcd カメラとLCD表示テスト(画像をLCDに表示する)

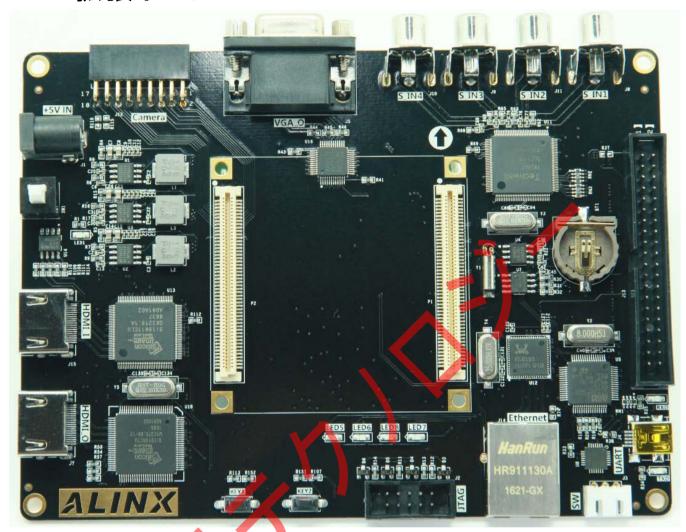

## 3.2 VGA インタフェース

ADI 社の ADV7123 を採用、VGA 信号を出力し、1080p@60Hz 出力をサポートする。

## FPGA ピン配置:

| VGA_CLK | K20 |

|---------|-----|

| VGA_EN  | F20 |

| VGA_HS  | F18 |

| VGA_VS  | J17 |

| VGA_R7  | T22 |

|        | 日外アクノロジーなら可能にす |

|--------|----------------|

| VGA_R6 | R22            |

| VGA_R5 | T21            |

| VGA_R4 | R20            |

| VGA_R3 | AB7            |

| VGA_R2 | AB8            |

| VGA_R1 | Y7             |

| VGA_R0 | AA8            |

| VGA_G7 | M22            |

| VGA_G6 | L22            |

| VGA_G5 | M21            |

| VGA_G4 | L20            |

| VGA_G3 | P22            |

| VGA_G2 | N22            |

| VGA_G1 | P21            |

| VGA_G0 | N20            |

| VGA_B7 | K17            |

| VGA_B6 | F <b>1</b> 9   |

| VGA_B5 | D21            |

| VGA B4 | C20            |

| VGA_B3 | D22            |

| VGA_B2 | C22            |

| VGA_B1 | G19            |

|        |                |

# 3.3 HDMI 出力インタフェース

VGA\_B0

HDMI 出力インターフェースは、Silion Image 社の SIL9134を採用、1080P@60Hz の出力、3D 出力をサポートする。

H19

SIL9134 の IIC インタフェースは STM32F103 と接続し、STM32F103 を通じて SIL9134 の初期化と制御をする。他のピンは FPGA と接続する。

FPGAピン配置:

9134 CLK Y12 9134 HS U22 9134 VS U20 V22 9134 DE 9134 D[0] Y18 9134\_D[1] U13 9134 D[2] W18 9134 D[3] U14 **AB18** 9134 D[4] AA18 9134 D[5] **AB17** 9134\_D[6] 9134 D[7] **AB14** 9134 D[8] Y17 9134 D[9] **AA14** 9134\_D[10] W13 9134 D[11] Y19 9134\_D[12] T19 9134 D[13] **AB19** 9134\_D[14] T20 9134 D[15] 117 9134\_D[16] W20 9134\_D[17] K18 9134\_D[18] W22 9134\_D[19] P19 9134 D[20] M19 9134 D[21] P20

9134 D[22]

9134 D[23]

N19

V21

# 3.4 HDMI 入力インタフェース

HDMI 入力インターフェースは、Silion Image 社の SIL9013を採用、1080P@60Hz の入力、多種のフォーマットのデータをサポートする。

SIL9013 の IIC インタフェースは STM32F103 と接続し、STM32F103 を通じて SIL9013 の初期化と制御をする。他のピンは FPGA と接続する。

FPGA ピン配置:

低価格、高品質が不可能? 日昇テクノロジーなら可能にする

AA12 9013 CLK **Y8** 9013 HS 9013 VS W8 9013 DE V7 9013 D[0] W10 9013\_D[1] W9 9013 D[2] Y10 9013 D[3] R8 Υ9 9013 D[4] 9013 D[5] R9 V11 9013\_D[6] 9013 D[7] AB9 9013 D[8] W11 9013 D[9] **AA10** 9013 D[10] **AB12** 9013\_D[11] **AB10** 9013 D[12] Y15 9013 D[13] W12 9013 D[14] **AB15** 9013 D[15] R11 9013 D[16] **AA16** 9013 D[17] T11 9013 D[18] W14 9013 D[19] V13 9013 D[20] W15 9013 D[21] Y14 9013\_D[22] Y16 9013 D[23] **AB16**

# 3.5 ビデオ入力インタフェース

Techwell 社の TW2867 を採用、4 チャネルのビデオ入力をサポート。PAL/NTSC/SECAM 自動認識し、BT656 出力、多チャネルでバス共用できる。

TW2867 の IIC インタフェースは STM32F103 と接続し、STM32F103 を通じて TW2867 の初期化と制御をする。他のピンは FPGA と接続する。

#### 回路図:

#### 実物イメージ:

#### FPGA ピン配置:

| · · · · · · · · · · · · · · · · · · · |            |

|---------------------------------------|------------|

| 2867_CLKP                             | C11        |

| 2867_CLKN                             | A11        |

| 2867_D[0]                             | A3         |

| 2867_D[1]                             | C5         |

| 2867_D[2]                             | A4         |

| 2867_D[3]                             | <b>A</b> 5 |

| 2867_D[4]                             | D6         |

| 2867_D[5]                             | B6         |

| 2867_D[6]                             | C6         |

| 2867 D[7]                             | <b>A</b> 6 |

# 3.6 ギガイーサネットインタフェース

Realtek RTL8211EG イーサネット PHY チップでネットワークを実現。

#### 回路図:

#### 実物イメージ:

#### FPGA ピン配置:

| ピン名称   | FPGA ピン | 説明           |

|--------|---------|--------------|

| E_GCLK | K19     | RGMII 送信クロック |

| E_TXD0 | E20     | 送信データ bit0   |

| E_TXD1 | E22     | 送信データ bit1   |

| E_TXD2 | D20     | 送信データ bit2   |

| E_TXD3 | F21     | 送信データ bit3   |

| E_TXEN | H18     | 送信イネーブル      |

| E_TXC  | G22     | MII 送信クロック   |

| E_RXC  | H21     | RGMII 受信クロック |

| E_RXDV | K21     | 受信データ有効信号    |

# 株式会社日昇テクノロジー

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

| E_RXD0  | J20 | 受信データ Bit0       |

|---------|-----|------------------|

| E_RXD1  | L19 | 受信データ Bit1       |

| E_RXD2  | H22 | 受信データ Bit2       |

| E_RXD3  | M20 | 受信データ Bit3       |

| E_CRS   | H20 | Carrier Sense 信号 |

| E_RESET | D19 | リセット信号           |

| E_MDC   | J19 | MDIO 管理クロック      |

| E_MDIO  | G20 | MDIO 管理データ       |

## 3.7 ARM コントローラ

拡張ボードに ARM チップ(STM32F103)を搭載。IO で各インタフェースチップをリセットし、I2C で各インタフェースチップのレジスタを設定し、FPGA とデータ通信を行う。

実物イメージ:

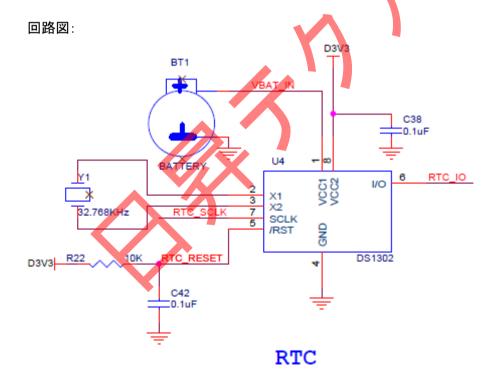

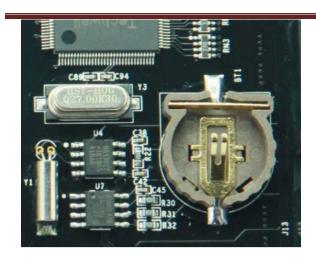

## 3.7.1 リアルタイムクロック

実物イメージ:

#### ARMピン配置:

| RTC_SCLK  | 15 |

|-----------|----|

| RTC_IO    | 16 |

| RTC_RESET | 14 |

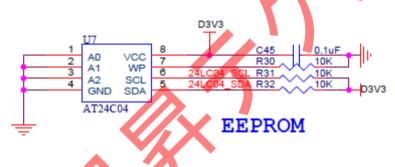

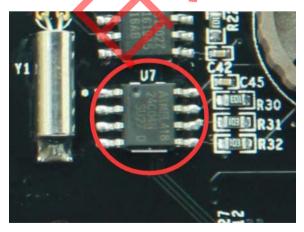

## **3.7.2 EEPROM**

## 実物イメージ

#### ARMピン配置:

| 24LC04_SDA | 59 |

|------------|----|

| 24LC04_SCL | 58 |

## 3.7.3 LED

#### 回路図:

# 3.7.4 USB シリアルポート

#### 回路図:

# 3.7.5 SD カード

ARM は SPI インタフェースで MicroSD カードと通信し、データの読取と保存を行う。

#### 実物イメージ:

#### ARMピン配置:

| TFCS   | 33 |

|--------|----|

| TFSCK  | 34 |

| TFMOSI | 36 |

| TFMISO | 35 |

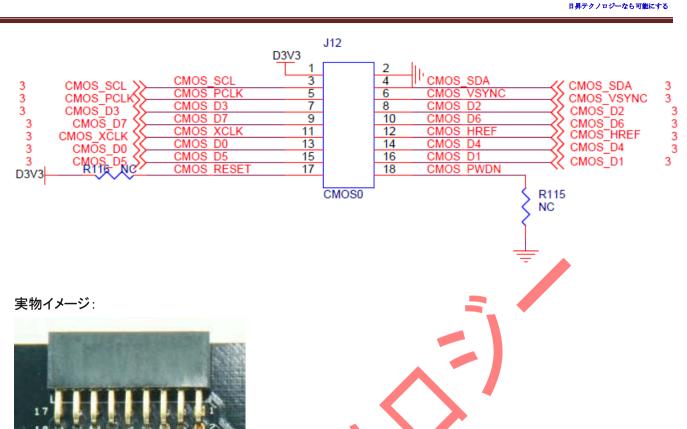

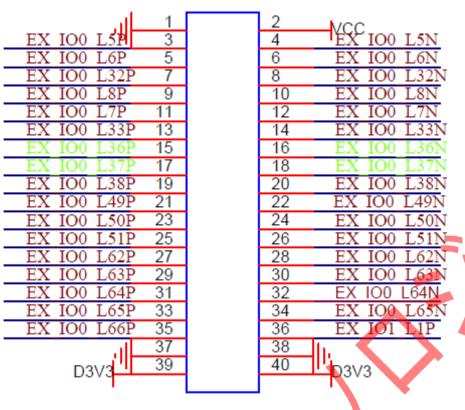

# 3.8 CMOS カメラ I/F

ボードの 18 ピンの CMOS カメラ I/F を搭載しております。 OV7670 カメラモジュール或いは OV5640 カメラモジュールと直結できる。 摂取した画像は HDMI 或いは VGA インタフェース経由で表示する。

#### 回路図:

Camera

低価格、高品質が不可能? 日昇テクノロジーなら可能にする

CMOS\_SCLK AB5 CMOS SDAT Y5 CMOS VSYNC AA4 CMOS HREF AB3 CMOS PCLK AB4 CMOS XCLK **Y**3 CMOS D[7] V9 CMOS D[6] U9 W6 CMOS\_D[5] CMOS D[4] AB<sub>6</sub> Y11 CMOS D[3] CMOS\_D[2] **AB11** CMOS\_D[1] Y6 CMOS D[0] AA6 **CMOS RESET**

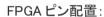

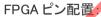

# 3.9 拡張インタフェース

**CMOS PWDN**

拡張ボードに 40 ピンの拡張インタフェースを搭載。5V 電源 1 チャネル、3.3V 電源 2 チャネル、GND は 3 チャネル、IO ポートは 34 チャネル。IO ポートは 5V デバイスと直結しては行けない、FPGA が壊れる恐れがある。5V デバイスを接続する場合はレベル変換チップを接続する必要。

J13

#### CON40A

#### 実物イメージ:

| 1  | GND  | 2  | VCC  |

|----|------|----|------|

| 3  | C7   | 4  | A7   |

| 5  | B8   | 6  | A8   |

| 7  | D7   | 8  | D8   |

| 9  | C9   | 10 | A9   |

| 11 | D9   | 12 | C8   |

| 13 | D10  | 14 | C10  |

| 15 | D11  | 16 | C12  |

| 17 | B12  | 18 | A12  |

| 19 | C13  | 20 | A13  |

| 21 | D14  | 22 | C14  |

| 23 | B14  | 24 | A14  |

| 25 | C15  | 26 | A15  |

| 27 | D15  | 28 | C16  |

| 29 | B16  | 30 | A16  |

| 31 | C17  | 32 | A17  |

| 33 | B18  | 34 | A18  |

| 35 | E16  | 36 | C19  |

| 37 | GND  | 38 | GND  |

| 39 | D3V3 | 40 | D3V3 |

# 3.10 JTAG インタフェース

#### 実物イメージ:

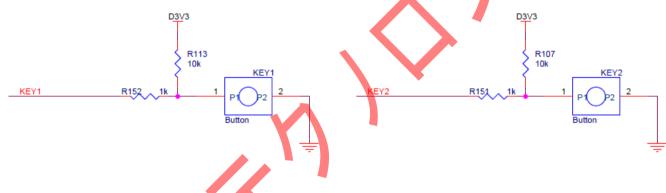

# 3.11 +-

ボードに2つのユーザーキーを搭載。

#### 回路図:

#### 実物イメージ:

#### FPGAピン配置:

| KEY1 | J22 |

|------|-----|

| KEY2 | K22 |

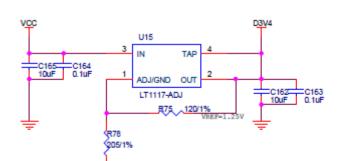

# 3.12 電源

3 チャネルの DC/DC 電源チップ MP1482 で 5V の入力電源を D3V3、D1V2、D1V8 を生成し、1 チャンルの LDO LT1117 で D3V4 電源を生成する。またコアボードにも給電する。

## 実物イメージ: