# Siga LCD Board ユーザーマニュアル

## 株式会社日昇テクノロジー

http://www.csun.co.jp info@csun.co.jp 作成日 2014/4/22

copyright@2014

日昇テクノロジーなら可能にする

## • 修正履歴

| NO | バージョン  | 修正内容 | 修正日       |

|----|--------|------|-----------|

| 1  | Ver1.0 | 新規作成 | 2014/4/22 |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

|    |        |      |           |

※ この文書の情報は、文書を改善するため、事前の通知なく変更されることがあります。 最新版は弊社ホームページからご参照ください。「http://www.csun.co.jp」

※ (株)日昇テクノロジーの書面による許可のない複製は、いかなる形態においても厳重に 禁じられています。

## 第一章 LCD Board の簡単な紹介

LCD Board は Siga-S16 開発ボードの画像マルチメディア拡張ボードである。ボードに 500 万画素の画像センサーモジュールと 4.3 インチの 24 ビットトゥルーカラーLCD スクリーンを搭載し、ユーザーに画像の収集、処理と表示のマルチメディアプラットフォームを提供する。FPGA の開発者はこのプラットフォームで各種の撮影、画像処理とデータ通信、画像表示などの機能を評価できる。

ユーザーに FPGA の Verilog 参考設計と詳しいプログラムの説明を提供している。開発者はこれらの参考 設計に基づき、素早く複雑のアプリケーションシステムを構築できる。製品の開発と発表を素早く実現できる。

LCD Board に画像収集と表示ソリューションを統合し、Siga-S16 Sparten6 開発ボードと配合し、ユーザーに全面的なPFGA 開発設計環境を提供している。LCD Board は工業制御、マルチメディアアプリケーション、IC 検証などに適用である。更に、大学の教材機械、FPGA トレーニング、個人の研究学習にも適用である。

図 1-1 LCD Board 開発ボード

低価格、高品質が不可能?

#### Siga LCD Board の主な特徴は下記の通り:

- LCD タッチスクリーンモジュール

- ◆ 4.3 インチの TFT-LCD モジュール (TMO43NBHO2) が付属し、解像度は 480\*272

- ◆ LED バックライトユニットが含まれる

- ◆ 24 ビット並列 RGB インターフェースを使用する

- ◆ タッチ機能回路を取っておき、タッチポイント X/Y の座標を相応のサンプリングポイントのデータに転換する。

#### 表 1-1 は LTC の主な物理仕様である (注意事項\*)

技術パラメータ 単位 仕様 LCD の寸法 4.3 inch 解像度 480 x3 (RGB) x 272 dot ドットピッチ 0.198(W) x 0.198(H) mm 活性化領域 95.04(W) x 53.86(H) モジュールのサイズ 105. 50 (W) x 67. 20 (H) x 2. 90 (D) mm 表面処理 Anti-Glare 重さ 44.065 g ポート Digital RGB 24 bits

表 1-1 LCD の主な物理仕様

- 500 万画素のデジタルイメージセンサモジュール

- ◆ 自動画像フォーカスと自動露出制御(AEC)

- ◆ 自動ホワイトバランス、自動 50/60 Hz の輝度検出

- ◆ プログラマブルフレームリフレッシュデータ

- ◆ 水平方向と垂直方向のミラーモード

- ◆ 列と行階層モード、サイズを調整する時画像質を改善する

- ◆ 列と行のスキップモード

- ◆ 異なる画像出力モードをサポートする: RAW RGB、RGB565/555/444、CCIR656、YUV422/420、YCbCr422と圧縮モード

- ◆ 標準なシリアル SCCB ポート制御

- ◆ パラレルデジタル Vidio ポート(DVP)と Dual Lane MIPI ポートモードをサポートする

表 1-2 は CMOS センサーの主なパラメータ:

#### 表 1-2 CMOS センサの主な性能パラメータ

| パラメータ         |                | 数值                     |  |  |

|---------------|----------------|------------------------|--|--|

| 有効画素          | 2592Hx1944V    |                        |  |  |

| 感知領域          | 1. 4umx1. 4um  |                        |  |  |

| 出力フォーマット      | 出力フォーマット       |                        |  |  |

| 入力 clock クロック |                | 6~27 MHz               |  |  |

| 最大スピード/メインク   | ロック周波数         | 96Mp/s at 96MHz        |  |  |

| 最大フレームレート     | QSXGA          | 15 fps                 |  |  |

|               | 1080p          | 30 fps                 |  |  |

|               | 1280x960       | 45 fps                 |  |  |

|               | 720p           | 60 fps                 |  |  |

|               | VGA (640x480)  | 90 fps                 |  |  |

|               | QVGA (320x240) | 120 fps                |  |  |

| ADC 解像度       |                | 12-bit                 |  |  |

| 感度            | 600mV/lux-sec  |                        |  |  |

| ダイナミック範囲      | 68 dB          |                        |  |  |

| SNR (maximum) | 36 dB          |                        |  |  |

| 電源電圧          | 供電電圧           | Core 1.5V, analog:2.8V |  |  |

| 電源電圧 I/0 電圧   |                | 1. 8V/2. 8V            |  |  |

# 第二章 LCD Board の概要

本節はシステムブロック図とパッケージを含め、Siga LCD Board の全体像を説明する。

## 2.1 レイアウトとパッケージ

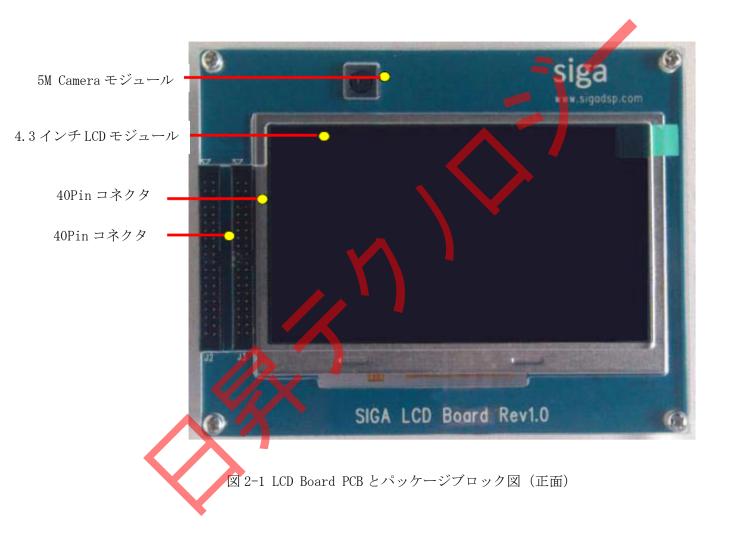

図 2-1 は LCD Board の正面の写真である。

低価格、高品質が不可能?

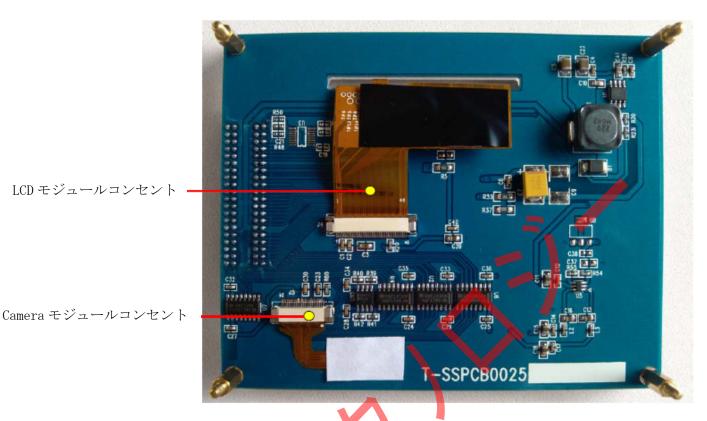

図 2-2 は LCD Board の背面の写真である。

図 2-2 LCD Board PCB とパッケージブロック図 (背面)

## 2.2 LCD Board システムプロック図

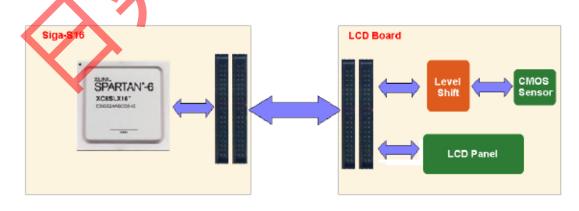

図 2-3 は LCD Board と Siga-S16 開発ボードの接続ブロック図。Sparten6 FPGA の拡張 IO を使用し LCD Board と直接に接続する。

図 2-3 LCD Board システムブロック図

# 第三章 Siga LCD Board の使用

本章はLCD Board と Siga-S16 開発ボードの接続とインタフェースの定義を紹介する。

## 3.1 LCD Board の設置

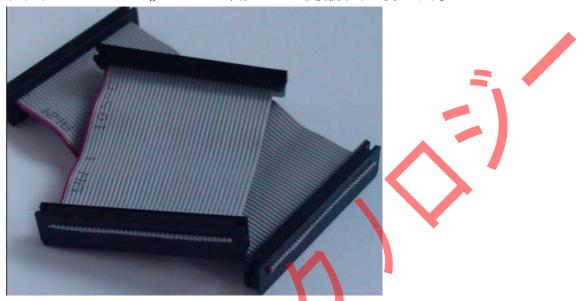

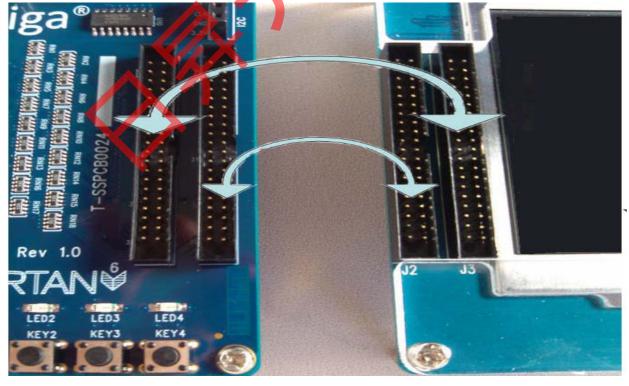

LCD Board と Siga-S16 FPGA 開発ボードの接続は 2 本の 40 ピンのフラットケーブルで実現する。デバッグする時 LCD Board と Siga-S16 FPGA 開発ボードを接続する必要がある。

2本のフラットケーブル、1本が短い、もう1本が長い。短いケーブルは FPGA 開発ボードの J4 と LCD Board の J2 と接続する、長いケーブルは FPGA 開発ボードの J3 と LCD Board の J3 と接続する。

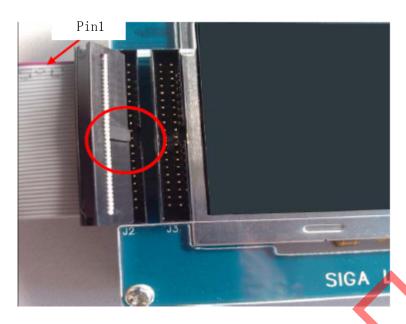

接続する時ケーブルのギャップの方向と 1Pin の位置にご注意ください。ケーブルを差し込む時は密接する様に奥まで押してください。

図 3-1 LCD ケーブル接続図

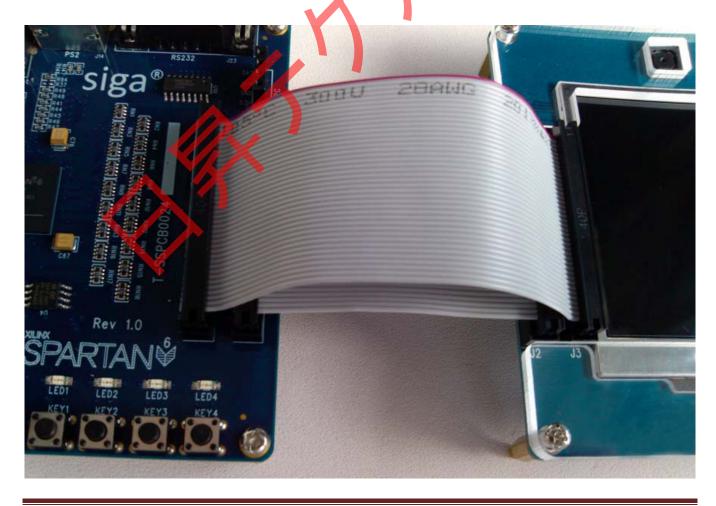

Siga-S16 開発ボードと LCD Board の接続後は図 3-2 の通り:

日展テクノロジーから可能にする

接続後 LCD board と SIga-S16 開発ボードを下図の通り積み上げるのもできる。

### 3.2 Pin の定義

以下はLCD Board の J2 と J3 のピンの定義、J2 の信号は Camera に接続する信号である。

Figure 3.3 the pin-out of the 40-pin connector (J2).

| Pin No.<br>(J2) | Pin Net<br>Name | Siga-S16 GPIO   | FPGA<br>Pin(U1) | Note          |

|-----------------|-----------------|-----------------|-----------------|---------------|

| 1               | Camera_reset    | EX_GPIO_B [0]   | L14             | Camera リセット信号 |

| 2               | Camera_pclk     | EX_GPIO_ B [1]  | L13             | クロックデータ信号     |

| 3               | Camera_xclk     | EX_GPIO_ B [2]  | L12             | Camera クロック信号 |

| 4               | Camera_pwnd     | EX_GPIO_ B [3]  | M18             | Power Down    |

| 5               | Camera_sdat     | EX_GPIO_ B [4]  | M16             | SCCB ポートデータ   |

| 6               | Camera_sclk     | EX_GPIO_ B [5]  | M14             | SCCB ポートクロック  |

| 7               | Camera_vsync    | EX_GPIO_ B [6]  | M13             | 列同期           |

| 8               | Camera_strob    | EX_GPIO_ B [7]  | N18             | 露光信号          |

| 9               | Camera_href     | EX_GPIO_ B [8]  | N17             | 行同期           |

| 10              | Camera_D7       | EX_GPIO_ B [9]  | N16             | Camera データ信号  |

| 11              | +5V             | -               | -               | Power         |

| 12              | GND             | -               | (2)             | Ground        |

| 13              | Camer_D6        | EX_GPIO_ B [10] | N15             | Camera データ信号  |

| 14              | Camer_D5        | EX_GPIO_ B [11] | N14             | Camera データ信号  |

| 15              | Camer_D4        | EX_GPIO_ B [12] | P18             | Camera データ信号  |

| 16              | Camer_D0        | EX_GPIO_ B [13] | P17             | Camera データ信号  |

| 17              | Camer_D3        | EX_GPIO_ B [14] | P16             | Camera データ信号  |

| 18              | Camer_D1        | EX_GPIO_ B [15] | T18             | Camera データ信号  |

| 19              | Camer_D2        | EX_GPIO_ B [16] | T17             | Camera データ信号  |

| 20-28           | NC              | -               | -               | NC            |

| 29    | +3.3V | - | - | Power  |

|-------|-------|---|---|--------|

| 30    | GND   | - | - | Ground |

| 31-40 | NC    | 2 | - | NC     |

Table 3.1 the pin-out of the 40-pin connector (J2).

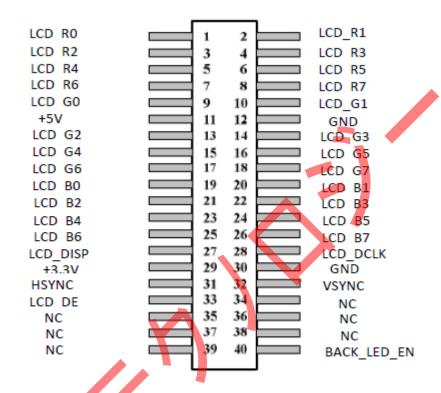

J3の信号はLCDモジュールに接続する信号。

Figure 3.4 the pin-out of the 40-pin connector (J3).

日昇テクノロジーなら可能にする

| Pin No.<br>(J3) | Pin Net<br>Name | Siga-S16 GPIO | FPGA<br>Pin(U1) | Note       |

|-----------------|-----------------|---------------|-----------------|------------|

| 1               | LCD_R0          | EX_GPIO_A [0] | C17             | LCD 赤色信号出力 |

| 2               | LCD_R1          | EX_GPIO_A [1] | C18             |            |

| 3               | LCD_R2          | EX_GPIO_A [2] | D17             |            |

| 4               | LCD_R3          | EX_GPIO_A [3] | D18             |            |

| 5               | LCD_R4          | EX_GPIO_A [4] | E18             |            |

| 6               | LCD_R5          | EX_GPIO_A [5] | E16             |            |

| 7               | LCD_R6          | EX_GPIO_A [6] | F18             |            |

| 8               | LCD_R7          | EX_GPIO_A [7] | F17             |            |

| 9               | LCD_G0          | EX_GPIO_A [8] | F16             | LCD 緑色信号出力 |

| 10              | LCD_G1          | EX_GPIO_A [9] | F15             |            |

| 11              | +5V             | -             | -               | Power      |

| 12              | GND             | -             | -               | Ground     |

| 13              | LCD_G2          | EX_GPIO_A[10] | F14             | LCD 緑色信号出力 |

| 14              | LCD_G3          | EX_GPIO_A[11] | G18             |            |

| 15              | LCD_G4          | EX_GPIO_A[12] | G16             |            |

| 16              | LCD_G5          | EX_GPIO_A[13] | G14             |            |

| 17              | LCD_G6          | EX_GPIO_A[14] | G13             |            |

| 18              | LCD_G7          | EX_GPIO_A[15] | H18             |            |

| 19    | LCD_B0      | EX_GPIO_A[16] | H17 | LCD 青色信号出力    |

|-------|-------------|---------------|-----|---------------|

| 20    | LCD_B1      | EX_GPIO_A[17] | H16 |               |

| 21    | LCD_B2      | EX_GPIO_A[18] | H15 |               |

| 22    | LCD_B3      | EX_GPIO_A[19] | H14 |               |

| 23    | LCD_B4      | EX_GPIO_A[20] | H13 |               |

| 24    | LCD_B5      | EX_GPIO_A[21] | H12 |               |

| 25    | LCD_B6      | EX_GPIO_A[22] | J18 |               |

| 26    | LCD_B7      | EX_GPIO_A[23] | J16 |               |

| 27    | LCD_DISP    | EX_GPIO_A[24] | J13 | LCD 表示イネーブル   |

| 28    | LCD_DCLK    | EX_GPIO_A[25] | K16 | LCD クロック出力    |

| 29    | +3.3V       |               | -   | Power         |

| 30    | GND         | -             | -   | Ground        |

| 31    | HSYNC       | EX_GPIO_A[26] | K18 | LCD 行同期信号     |

| 32    | VSYNC       | EX_GPIO_A[27] | K17 | LCD 列同期信号     |

| 33    | LCD_DE      | EX_GPIO_A[28] | K15 | LCD データ出力有効信号 |

| 34-39 | NC          | -             | -   | _             |

| 40    | BACK_LED_EN | EX_GPIO_A[35] | L15 | バックライト回路制御    |

Table 3.2 the pin-out of the 40-pin connector (J3)

# 第四章 LCD Board 設計例と資料

本章はSiga-S16 開発キットでLCD 画像表示と撮影を実現する設計例を紹介する。

## 4.1 システム要求

これらの設計例を実行、コンパイルするために、下記の内容が必要である:

- Siga-S16 開発ボードと LCD Board

- 提供されたサンプルフォルダとディレクトリの全ての内容を PC にコピーする

- PCに ISE13.1或いは更に高いバージョンのソフトウェアをインストールする

#### 4.2 LCD Board 設計例

#### 設計例 1:LCD 画像表示

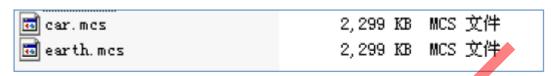

この設計例は FPGA 内部のテスト画像と SPI flash に保存する画像を表示する。テストする前に画像データを SPI Flash にダウンロードする必要がある。付属 DVD に画像データが保存された MCS ファイル (car. mcs  $^{2}$  earth. mcs) が提供される。

Figure 4.2 MCS File For LCD Display

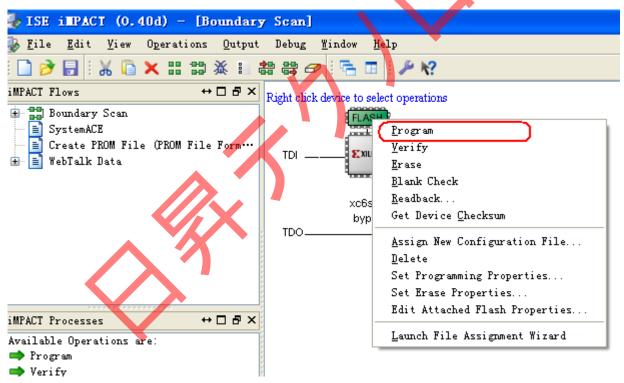

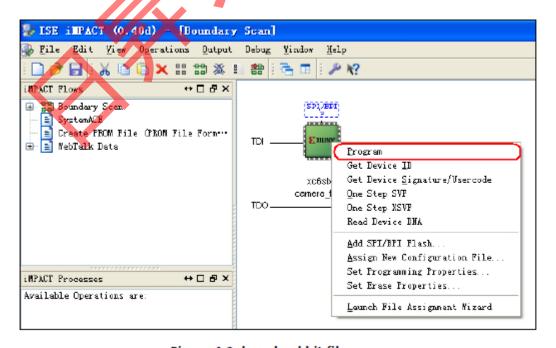

ここでは car. mcs を例にして紹介する。先ずは iMPACT ツールを使用し car. mcs ファイルを Siga-S16 開発ボードの SPI-Flash にダウンロードする。

Figure 4.2 Program SPI Flash

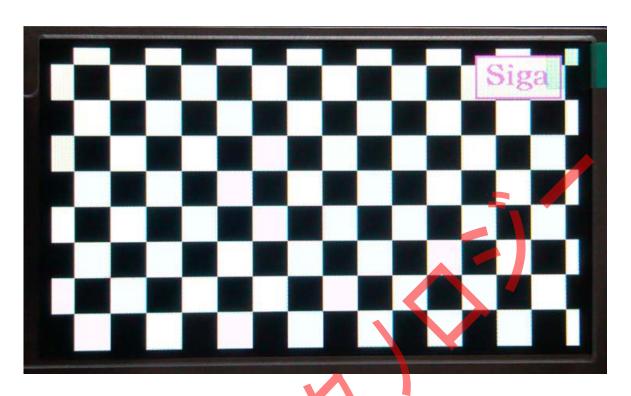

ダウンロード後、Siga-S16 開発ボードの Key1 ボタンを押して LCD の表示画像を切り換える。

● 格子像を表示する

グラデーション画像を表示する

● FLASH の画像を表示する

設計例 2: Camera 画像収集と表示

iMPACT ツールを使用しディレクトリ¥Verilog¥camera\_test のファイル camera\_top. bit を FPGA にダウンロードする。

Figure 4.3 download bit file

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

ダウンロード後、LCD にリアルタイムで camera モジュールが収集した画像を表示する。Siga-S16 開発ボードの Key1 ボタンを押せば、ダイナミック表示モードが終了し、LCD はスタティックにボダンを押す時収集した画像を表示する。

Figure 4.4 Display Camera photo

## 4.3 資料

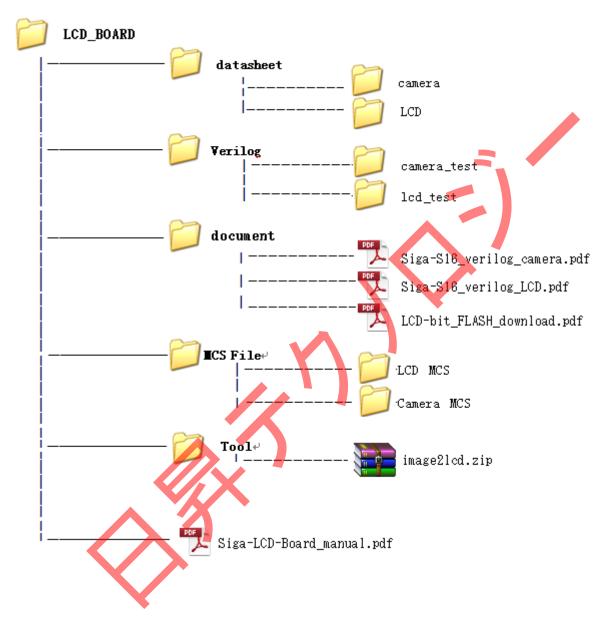

Siga LCD Board の資料ディレクトリの構成は下図の通り:

以上。