## VIP\_Full FPGA ビデオ開発ボード 快速入門ガイド

株式会社日昇テクノロジー

http://www.csun.co.jp

info@csun.co.jp

作成日 2015/03/16

copyright@2015

低価格、高品質が不可能? 日昇テクノロジーなら可能にする

## • 修正履歷

| NO | バージョン  | 修正内容 | 修正日        |

|----|--------|------|------------|

| 1  | Ver1.0 | 新規作成 | 2015/03/16 |

|    |        |      |            |

|    |        |      |            |

|    |        |      |            |

|    |        |      |            |

|    |        |      |            |

|    |        |      |            |

|    |        |      |            |

|    |        |      |            |

※ この文書の情報は、文書を改善するため、事前の通知なく変更されることがあります。

最新版は弊社ホームページからご参照ください。「http://www.csun.co.jp」

※ (株)日昇テクノロジーの書面による許可のない複製は、いかなる形態においても厳重に 禁じられています。

低価格、高品質が不可能?

#### 日昇テクノロジーなら可能にする

#### 目次

| 1. | VIP_Full FPGA ビデオ開発ボード機能概要 | . 4 |

|----|----------------------------|-----|

| 2. | VIP_Full FPGA ビデオ開発ボードのテスト | . 7 |

| 3. | サンプルソースについて                | 11  |

| 1  | サンプルソース プロジェクトのディレクトリー     | 1 2 |

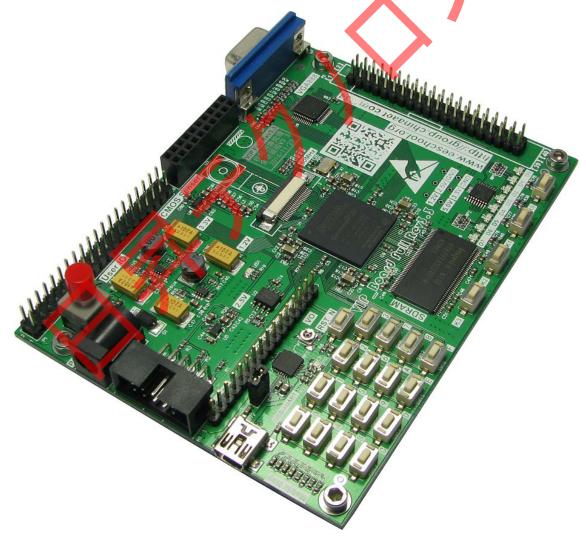

## 1. VIP\_Full FPGA ビデオ開発ボード機能概要

本開発ボードのメインマイコンはAltera Cyclone IVシリーズのFPGAを利用している。

Cyclone IIシリーズのFPGAと比べ、下記の特徴がある。

| 特徴         | Cyclone II          | Cyclone IV                 |

|------------|---------------------|----------------------------|

| 最適コストアーキテク | コストはCyclone FPGAより  | コストはCyclone II FPGAより20%オフ |

| チャ         | 30%オフ               | 消費電力はCycloneII FPGAより65%オフ |

| プロセステクノロジー | 90-nm               | 65-nm TSMC低消費電力            |

| コア電圧       | 1. 2V               | 1. 2V                      |

| I/0電圧      | 1.5V、1.8V、2.5V、3.3V | 1.5V、1.8V、2.5V、3.3V        |

| ロジック集積度    | LE: 4680~68416個     | LE: 6272~114480個           |

| I/0ピン数     | 85-622              | 80-529                     |

| 組込み式メモリ    | M4K 最大容量:1Mbit      | M9K 最大容量:4Mbit             |

ホームページ: http://www.csun.co.jp

メール: info@csun.co.jp

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

| 外部メモリインターフ | SDR, DDR, DDR2, QDRII | SDR、DDR、DDR2、QDRII         |

|------------|-----------------------|----------------------------|

| ェースサポート    |                       |                            |

| デジタル信号処理   | 18*18の乗算器最大150個       | 18*18の乗算器最大288個            |

| (DSP)      |                       |                            |

| PLL        | PLL:2~4、一つのPLLは3チ     | PLL:2~4、一つのPLLは5チャンネルの出力をサ |

|            | ャンネルの出力をサポー           | ポート                        |

|            | F                     | PLLはカスケード接続、ダイナミックコンフィグ    |

|            |                       | ができる                       |

| クロックネットワーク | 最大16個の専用グローバ          | 最大20個の専用グローバル・クロック         |

|            | ル・クロック                |                            |

本開発ボードは15000LEリソースを持っているEP4CE15E17C8Nをメインマイコンとして採用。 EP4CE15E17C8N FPGAのリソース:

| LE    | ユーザーI0 | メモリ        | 乗算器 | PLL | グローバスクロック |

|-------|--------|------------|-----|-----|-----------|

| 15408 | 166    | 516096Bits | 112 | 4   | 20        |

VIP\_Fullボードは256のBGAパッケージのFPGAを搭載。このFPGAのPLLはカスケード接続でき、ダイナミックコンフィグ機能を持っているから、Global clockを20個作成できることにより、ユーザーにもっとフレキシブルな設計を提供できる。内蔵乗算器112個、31.5K\*16Bitのメモリでチップ内蔵のリソースを増やした。またCyclone IVシリーズのFPGAはReal LVDS Interfaceなどのハードウエアリソースを持っている。

#### VIP Fullボードの主か機能・

| No. | 機能モジュール     | 機能概要                                                 |

|-----|-------------|------------------------------------------------------|

| 1   | FPGA        | Altera Cyclone IVシリーズFPGAをCPUとして採用                   |

|     |             | EP4CE15E17C8N: LEs: 1.5万 ユーザーIO: 166                 |

| 2   | VGAモジュール    | ADV/GM7123で <mark>2</mark> 4BitのTFT VGAインターフェース回路を実現 |

|     |             | し、ビデオ画像のディスプレイインターフェイスとする                            |

| 3   | SDRAMモジュール  | Hynixの32Bit SDRAM HY57V283220Tを搭載                    |

|     |             | 4Banks*1M*32Bitの内24bitのリソース使用。ビデオ画像の                 |

|     |             | メモリとする                                               |

| 4   | CMOSカメラモジュー | 一般市販のFPCインターフェースのCMOS Sensorをサポート。                   |

|     | ル1          | デフォルトモジュール:30W画素のOV7725-FPC                          |

| 5   | CMOSカメラモジュー | 0V7725カメラモジュールと直結で利用できる                              |

|     | ル2          |                                                      |

| 6   | 電源モジュール     | MP2214DCDCソリューションを採用し、USB通信及び給電を行                    |

|     |             | う。定格ヒューズ:500mA電流でPCをプロテクトできる                         |

| 7   | FLASH       | EPCS4/M25P40シリアルSPI FLASHを利用。1W LEs FPGAのロ           |

|     |             | ジックコード処理に4Mbitの容量は十分                                 |

| 8   | クリスタル       | 50MHzクリスタルを搭載し、FPGAのクロックソースにする                       |

| 9   | キーモジュール     | (1) グローバルリセットキー1つ                                    |

|     |             | (2) ユーザーキー4つ                                         |

|     |             | (3) 4*4のマトリックスキーボード                                  |

ホームページ: <u>http://www.csun.co.jp</u>

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

| 10 | LED         | ボードに8つのLEDを搭載され、74HC595で3線式シリアルコ    |

|----|-------------|-------------------------------------|

|    |             | ンフィグを実現                             |

| 11 | LCD1602     | LCD1602回路を搭載し、8*5ミリ型LCD1602を採用      |

|    |             |                                     |

| 12 | ユーザーI0      | 独立のユーザーI0を35個引き出し、柔軟性を高める           |

| 13 | DB-40インターフェ | VGAと共有のDB-40インターフェースを引き出し、LCDコント    |

|    | ース          | ロール基板とのインターフェースとして利用                |

| 14 | JTAGインターフェー | 標準Altera JTAGインターフェース、sofテストとjicファー |

|    | ス           | ムウェア書き込みをサポート                       |

低価格、高品質が不可能? 日昇テクノロジーなら可能にする

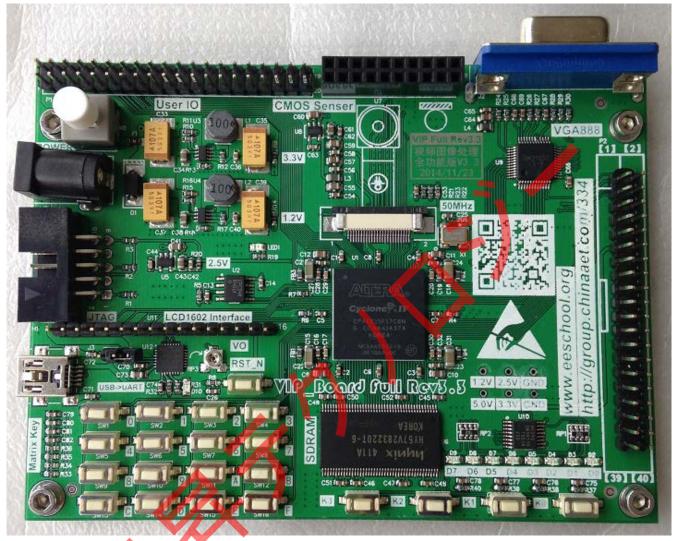

## 2. VIP\_Full FPGA ビデオ開発ボードのテスト

出荷状態で、ボードに既にファームウェアが書き込まれている。すべての周辺機器のドライバがあり、ボード機能のテストができる。

USB給電あるいは5Vアダプター給電を利用できる。USB給電の場合、消費電力は212mAである。

※5Vアダプター給電と比べてLCD1602のコントラストが少し低い。

※5インチLCD接続する時は不安定の可能性があり、お勧めしない。

5Vアダプター給電の場合、電流、電圧などの問題を考慮しなくてもいい。すべての周辺機器が起動している場合の消費電力は1W++である。

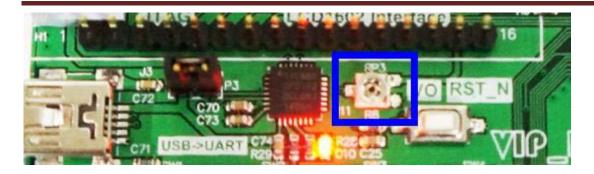

ジャンパーでUSB/5Vアダプター給電を選択できる。ジャンパーをショートにするのはUSB給電設定である。 デフォルトは5Vアダプター給電に設定する(USB→UART機能を利用する)場合、ジャンパーを外す。

#### (1) 0V7725モジュールを繋ぐ。

FPC貼り付け式/0V7725モジュールのうちの1つを接続すればいい。

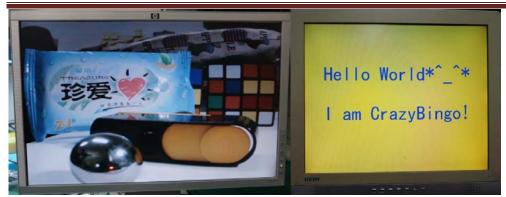

VGAケーブルを接続すると、ディスプレーにカメラがキャプチャした画像が表示される。

低価格、高品質が不可能が

日昇テクノロジーなら可能にする

ビデオが7秒再生した後、第8秒に「Hello World^-^, I am CrazyBingo!」の文字列が表示される。 上記正しい現象でしたら、CMOS回路及びVGA回路部分は正常に動作している。

- (2) キーの操作で8つのLEDの動作は以下のようになる:

- a. D8-D5 (4つのLED) は循環に点滅する。

- B. D4-D0は4Bitの独立キー(0001.0010.0100.1000) あるいは4\*4マトリックスキーボード(0→F) でコントロールされる

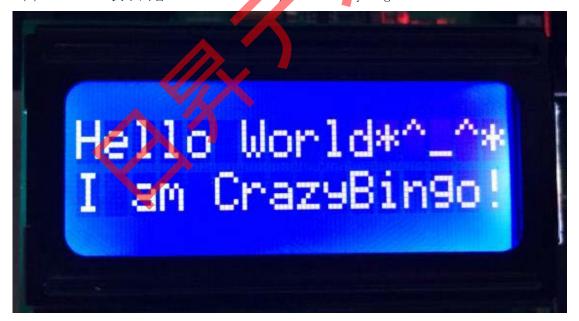

(3) LCD1602の表示内容: Hello World へ, I am CrazyBingo!

コントラストが十分ではないと思われる場合、プラスドライバーでLCD1602下のポテンショメーターを回して、コンラストを調節するといい。

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

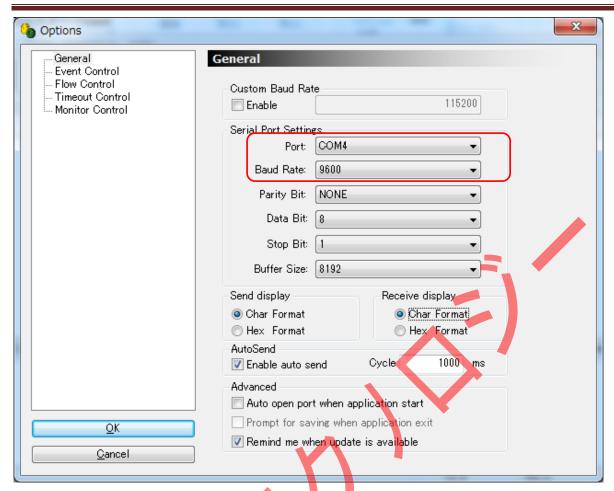

(4) CP2102 シリアルドライバをインストールする。シリアルデバッグツールを開き、データを送信して USB-UART モジュールをテストする。

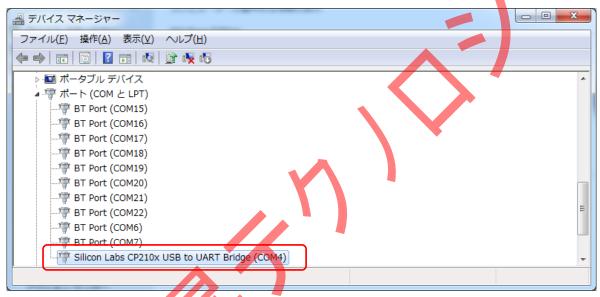

CP2102のドライバをインストールする(tool¥CP2102\_driver)。

インストール終了後、デバイスマネージャーに認識されたデバイスが表示される。

シリアルデバッグツールを開き、ボーレートを 9600、1000ms ごと送信に設定:

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

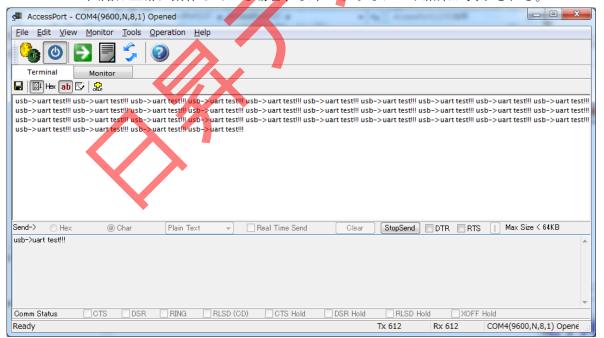

USB→UART 回路は正常に動作している場合、以下のようなテスト結果が表示される。

低価格、高品質が不可能? 日昇テクノロジーなら可能にする

## 3. サンプルソースについて

各サンプルについての詳細の説明は付属DVDにある「VIP\_Full\_FPGA\_Camera\_manual.pdf」をご参照ください。ボードのFPGAコードサンプルに下記の2つの部分が含まれている。

■HDL-Logic: HDL-Logi Examples

Verilog HDLに基づき、基本的な周辺機能を実現する。

・サンプルリスト:

| No. | プロジェクト                             | 説明                                 |

|-----|------------------------------------|------------------------------------|

| 1   | 01_Counter_Design                  | 4Bit カウンタ実験                        |

| 2   | 02-1_LED_Display_Design_8BitAddr   | 8BitLED 表示実験                       |

| 3   | 02-2_LED_Display_Design_595Addr    | 74HC595 に基づくシリアル 8BitLED 表示実験      |

| 4   | 02-3_LED_Display_Design_595Water   | 74HC595 に基づくシリアル 8Bit              |

|     |                                    | sequentially illuminated LEDs 表示実験 |

| 5   | 02-4_LED_Display_Design_595Breathe | 74HC595に基づくシリアル 8Bit Breath LED 表  |

|     |                                    | 示実験                                |

| 6   | 03-1_KEY_Scan_design_Jitter        | 遅延に基づく独立キーのシェイク防止検知実               |

|     |                                    | 験                                  |

| 7   | 03-2_KEY_Scan_design_Counter       | カウントに基づく独立キーのシェイク防止検               |

|     |                                    | 知実験                                |

| 8   | 03-3_KEY_Scan_design_Matrix        | カウントに基づく独立キーのシェイク防止検               |

|     |                                    | 知実験                                |

| 9   | 04_LCD41620_Display_design         | ロジックにより実現された LCD1602 表示実験          |

| 10  | 05-1_System_Ctrl_Design            | PLL 抜きのグローバスクロック管理モジュー             |

|     |                                    | ルの設計                               |

| 11  | 05-2_System_Ctrl_Design_PLL        | PLL 付きのグローバスクロック管理モジュー             |

|     |                                    | ルの設計                               |

| 12  | 07_PC2FPGA_UART_Test               | UART プロトコルに基づく FPGA と PC の通信       |

| 13  | 08-1_VGA_Display_Test_640480       | 640*480@60Hz VGA ドライバ表示実験          |

| 14  | 08-2_VGA_Display_Test_12801024     | 1280*1024@60Hz VGA ドライバ表示実験        |

| 15  | 09-1_VGA_Char_Display_Test         | VGA 文字表示実験                         |

| 16  | 09-2_SDRAM_VGA_Display_Test640480  | SDRAMに基づく VGA コントローラ設計及びテス         |

|     | <b>X</b> /                         | F                                  |

| 17  | 10_CMOS_0V7725_RGB640480           | VGA に基づく OV7725 RGB ビデオキャプチャー      |

|     | •                                  | 表示システム                             |

#### ■HDL-VIP: HDL-VIP Example

Verilog HDLに基づき、HDLに基づくVideo Image Processorビデオ画像アルゴリズムのハードウエア加速処理を実現する。

・サンプルリスト:

| No. | プロジェクト                         | 説明                       |

|-----|--------------------------------|--------------------------|

| 1   | 11_CMOS_OV7725_RGB888_YCbCr444 | RGB888⇒YCbCr444 アルゴリズムの実 |

|     |                                | 現                        |

ホームページ: http://www.csun.co.jp

メール: info@csun.co.jp

低価格、高品質が不可能?

日昇テクノロジーなら可能にする

| 2 | 12_CMOS_0V7725_YCbCr422_RGB888             | YCbCr422⇒RGB888アルゴリズムの実<br>現                                |

|---|--------------------------------------------|-------------------------------------------------------------|

| 3 | 13_CMOS_0V7725_Gray_Mean_Filter            | OV7725に基づくグレースケール画像                                         |

| 4 | 14_CMOS_0V7725_Gray_Median_Filter          | の平均フィルタアルゴリズムの実現<br>0V7725に基づくグレースケール画像<br>のメジアンフィルターアルゴリズム |

|   |                                            | の実現                                                         |

| 5 | 15_CMOS_0V7725_Gray_Sobel                  | 0V7725に基づくグレースケール画像<br>のSoble縁検知アルゴリズムの実現                   |

| 6 | 16_CMOS_OV7725_Gray_Sobel_Erosion          | グレースケール画像のSoble+浸食演算アルゴリズムの実現                               |

| 7 | 17_CMOS_OV7725_Gray_Sobel_Erosion_Dilation | グレースケール画像のSoble+浸食演<br>算+膨張演算アルゴリズムの実現                      |

| 8 | 18_CMOS_OV7725_RAW8_RGB888                 | 0V7725に基づくBayer配列画像の回復         アルゴリズムの実現                    |

低価格、高品質が不可能で

日昇テクノロジーなら可能にする

# **4.** サンプルソース プロジェクトのディレクトリー説明

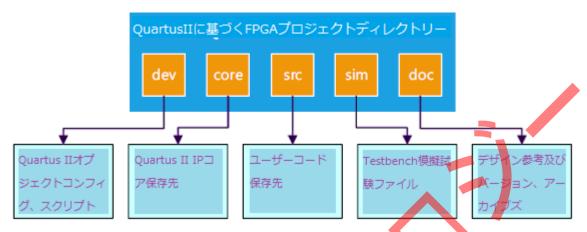

■フレームワーク図:

- 一つのQuartus IIオプジェクトに5つの部分が含まれている。

- ・dev オプジェクトセットアップ後、そのままにしておく

- ・core 設計時、Quartus II IPコアの保存先

- ・src 新規作成したVerilog HDLファイルの保存先

- ・Sim Modelsim模擬試験オプジェクトの保存先。一つのオプジェクトに複数の試験サブモジュールがある場合、Simで層化される

- ・doc 設計のアーカイブズ、参考などの情報:改版、更新及びチームワークで改善すべき部分 類似のフレームワークは他のプロセッサの設計にも適用している。これはただQuartus IIに活用する典型 的なサンプルである。